- 您现在的位置:买卖IC网 > PDF目录69345 > SPC5634MF0MLQA8 (FREESCALE SEMICONDUCTOR INC) FLASH, 80 MHz, MICROCONTROLLER, PQFP144 PDF资料下载

参数资料

| 型号: | SPC5634MF0MLQA8 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | FLASH, 80 MHz, MICROCONTROLLER, PQFP144 |

| 封装: | 20 X 20 MM, 0.50 MM PITCH, 1.40 HEIGHT, ROHS COMPLIANT, LQFP-144 |

| 文件页数: | 72/122页 |

| 文件大小: | 1173K |

| 代理商: | SPC5634MF0MLQA8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页当前第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页

Pinout and signal description

MPC5634M Microcontroller Data Sheet, Rev. 6

Freescale Semiconductor

53

2.7

Signal details

Table 5 contains details on the multiplexed signals that appear in Table 3, “MPC563xM signal properties.”

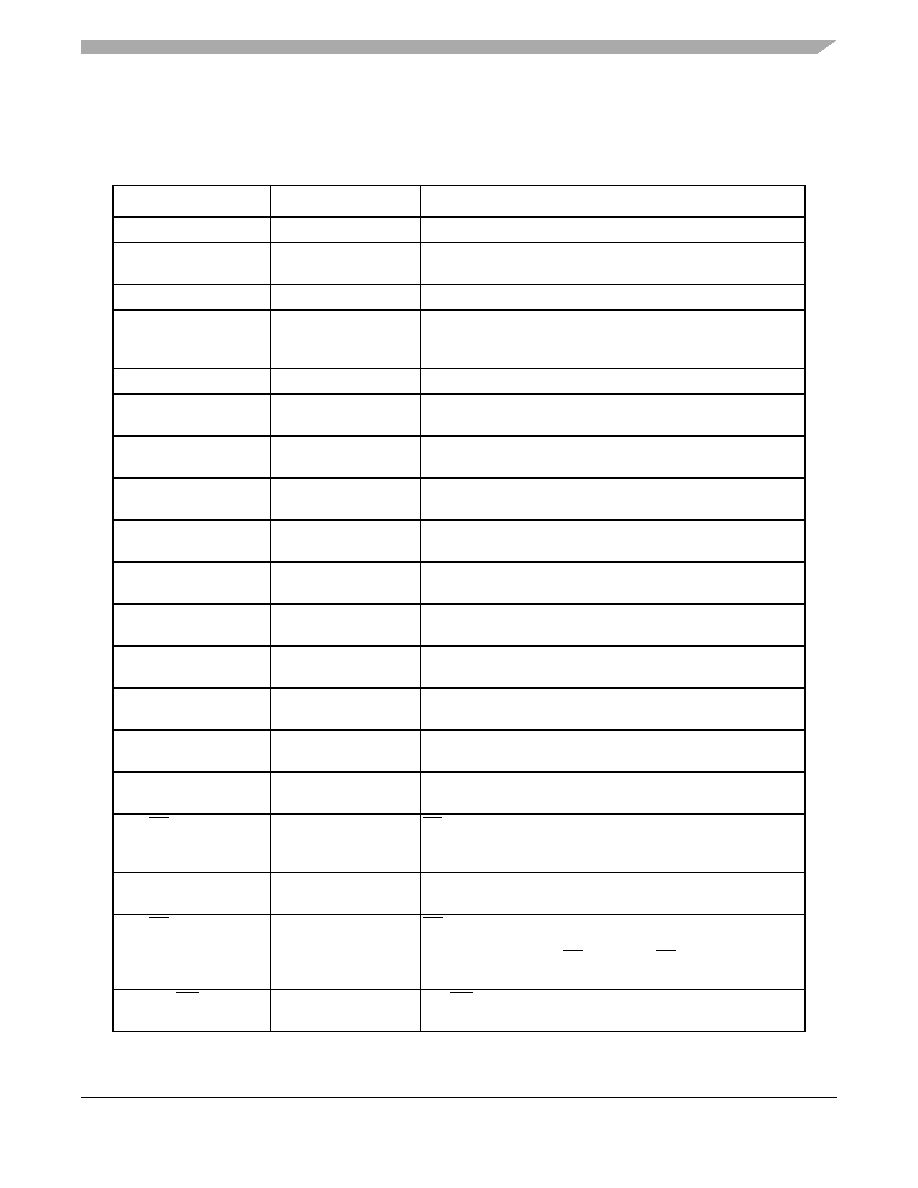

Table 5. Signal details

Signal

Module or Function

Description

CLKOUT

Clock Generation

MPC5634M clock output for the external/calibration bus interface

EXTAL

Clock Generation

Input pin for an external crystal oscillator or an external clock

source based on the value driven on the PLLREF pin at reset.

EXTCLK

Clock Generation

External clock input

PLLREF

Clock Generation

PLLREF is used to select whether the oscillator operates in xtal

mode or external reference mode from reset. PLLREF=0 selects

external reference mode.

XTAL

Clock Generation

Crystal oscillator input

SCK_B_LVDS-

SCK_B_LVDS+

DSPI

LVDS pair used for DSPI_B TSB mode transmission

SOUT_B_LVDS-

SOUT_B_LVDS+

DSPI

LVDS pair used for DSPI_B TSB mode transmission

SCK_C_LVDS-

SCK_C_LVDS+

DSPI

LVDS pair used for DSPI_C TSB mode transmission

SOUT_C_LVDS-

SOUT_C_LVDS+

DSPI

LVDS pair used for DSPI_C TSB mode transmission

PCS_B[0]

PCS_C[0]

DSPI_B - DSPI_C

Peripheral chip select when device is in master mode—slave

select when used in slave mode

PCS_B[1:5]

PCS_C[1:5]

DSPI_B - DSPI_C

Peripheral chip select when device is in master mode—not used

in slave mode

SCK_B

SCK_C

DSPI_B - DSPI_C

DSPI clock—output when device is in master mode; input when

in slave mode

SIN_B

SIN_C

DSPI_B - DSPI_C

DSPI data in

SOUT_B

SOUT_C

DSPI_B - DSPI_C

DSPI data out

CAL_ADDR[12:30]

Calibration Bus

The CAL_ADDR[12:30] signals specify the physical address of

the bus transaction.

CAL_CS[0:3]

Calibration Bus

CSx is asserted by the master to indicate that this transaction is

targeted for a particular memory bank on the Primary external

bus.

CAL_DATA[0:15]

Calibration Bus

The CAL_DATA[0:15] signals contain the data to be transferred

for the current transaction.

CAL_OE

Calibration Bus

OE is used to indicate when an external memory is permitted to

drive back read data. External memories must have their data

output buffers off when OE is negated. OE is only asserted for

chip-select accesses.

CAL_RD_WR

Calibration Bus

RD_WR indicates whether the current transaction is a read

access or a write access.

相关PDF资料 |

PDF描述 |

|---|---|

| SPC5632MF0MLQA6 | FLASH, 60 MHz, MICROCONTROLLER, PQFP144 |

| SPC563M54L3COBY | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP100 |

| SPC563M60L3COCY | 32-BIT, FLASH, 80 MHz, MICROCONTROLLER, PQFP100 |

| SPC563M54L3COCY | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP100 |

| SPC563M60L3COAR | 32-BIT, FLASH, 80 MHz, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SPC5634MF0MLUA4 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:microcontroller units (MCUs) |

| SPC5634MF0MLUA6 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:microcontroller units (MCUs) |

| SPC5634MF0MLUA8 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High performance e200z335 core processor |

| SPC5634MF0MMGA4 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:microcontroller units (MCUs) |

| SPC5634MF0MMGA6 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:microcontroller units (MCUs) |

发布紧急采购,3分钟左右您将得到回复。