- 您现在的位置:买卖IC网 > PDF目录98144 > ST62P35BQ1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 PDF资料下载

参数资料

| 型号: | ST62P35BQ1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| 封装: | PLASTIC, QFP-52 |

| 文件页数: | 39/82页 |

| 文件大小: | 617K |

| 代理商: | ST62P35BQ1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

44/82

ST62T35B/E35B

CENTRAL COUNTER (Cont’d)

4.3.1.3 Capture functions

Content of the counter CT can always be down-

loaded (captured) into the CP register at selecta-

ble event occurrence on pins CP1 and CP2, while

capture in RLCP is possible only when the bit

RELOAD is cleared.

Capture functions with RELOAD cleared are used

for period or pulse width measurements with input

CP2, or for phase measurements between two

signals on CP1 and CP2, with the counter in free

running mode. In these modes, counter values by

the two events occurence are stored into RLCP

and CP and the counter remains in free running

mode.

Capture functions with RELOAD set, are used for

same application purpose, but in that case, the

first event reloads the counter from RLCP while

the second event captures the counter content

into the CP register. Therefore, the counter is not

in free running mode for other functions since the

down counting start is initiated by either CP1, CP2

or RUNRES event according to RLDSEL1 and

RLDSEL2 bit.

4.3.2 SIGNAL GENERATION MODES

4.3.2.1 Output modes

Any

positive

comparison

to

0000h

or

MASK&CMP, and any overflow occurence can be

used to control the OVF or PWM output pins in

various modes defined by bits OVFMD, PWM-

POL, PWMEN and PWMMD.

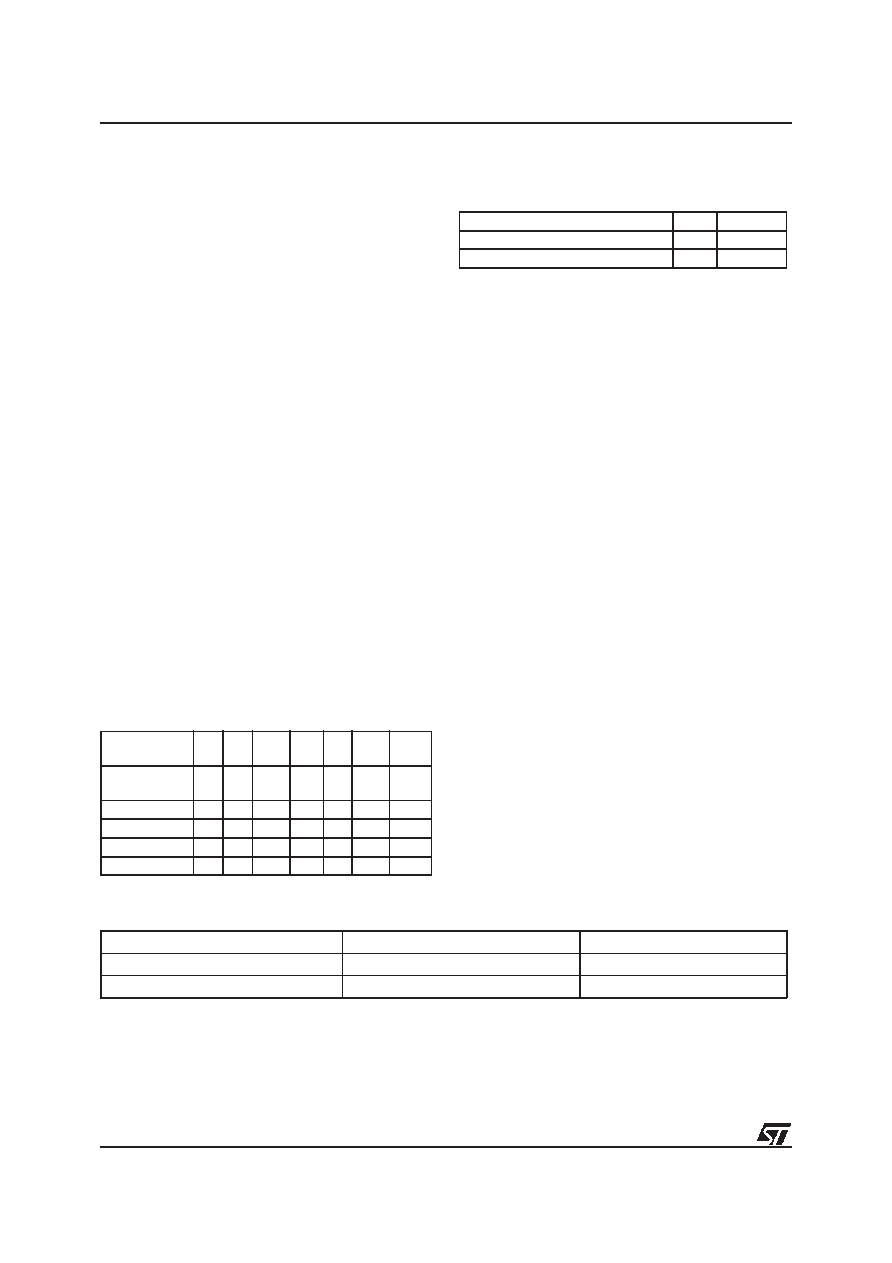

PWM pin output modes

OVF pin output modes

* The OVF pin is reset by clearing the flag OVF-

FLG.

4.3.2.2 Frequency and duty cycles on PWM

pins

In Set/Reset mode (PWMMD=0), the period on

the PWM pin is the time between two matched

masked comparison to 0000h, at which PWM pin

is set (PWMPOL=1) or reset (PWMPOL=0). As

long as no reload function from RLCP is per-

formed (RELOAD bit cleared) and no mask is

used, this value is 2

16 x Psc x Tclk. If, on the con-

trary, reload function or a mask are used, the fre-

quency is controlled through the RLCP and MASK

values (Figure 25.). The condition to reset (PWM-

POL=1) or set back (PWMPOL=0) PWM pin is a

matched masked comparison to CMP. Given a

RLCP and MASK values within the Table 1, CMP

defines the duty cycle.

In Toggle mode (PWMMD=1), PWM pin changes

of state at each positive masked comparison to

CMP value. The frequency is half the frequency in

Set/Reset mode and the duty-cycle is always

50%.

4.3.2.3 Frequency and duty cycles on OVF pin

OVF pin activation is directed by the timer over-

flow occurence and therefore its frequency de-

pends only of the downcounting time from the re-

load value to 0000h. This means its period is

equal to T= (RLCP+1) x Psc x Tclk in Set/Reset

mode and 2 x (RLCP+1) x Psc x Tclk in Toggle

mode.

Duty cycle is controlled in Set/Reset mode

(OVFMD cleared) by software, since OVF pin can

be reset only by clearing the OVFFLG bit. In tog-

gle mode (OVFMD set), the duty cycle is always

50%.

Achievable periods on PWM pin

Note: n is the position of the most significant bit of MASK value.

MASK & CNT

= 0000h

x

no

yes

no

yes

X

MASK&CT=

MASK&CMP

x

yes

no

yes

no

yes

PWMEN

0

1

PWMMD

X

0

1

PWMPOL

0

1

0

1

X

PWM pin

0

1

Reset Set

Set Reset Toggle

Zero overflow (OVFFLG)

1

OVFMD

0

1

OVF pin

Set*

Toggle

Mask value

FFFFh

xxxxh

Period in Set/Reset mode (PWMMD=0)

(RLCP+1) x Psc x Tclk

2

(n+1) x Psc x Tclk

Period in Toggle mode (PWMMD=1)

2 x (RLCP+1) x Psc x Tclk

2 x 2

(n+1) x Psc x Tclk

43

相关PDF资料 |

PDF描述 |

|---|---|

| ST6235BQ1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| ST62P45BQ6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| ST62T03CM6E | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST62T10BM6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST62T25BB6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62P52C | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MOMTR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MPITR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MSATR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CN6/MMMTR | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。