- 您现在的位置:买卖IC网 > PDF目录98144 > ST62P35BQ1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 PDF资料下载

参数资料

| 型号: | ST62P35BQ1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| 封装: | PLASTIC, QFP-52 |

| 文件页数: | 55/82页 |

| 文件大小: | 617K |

| 代理商: | ST62P35BQ1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

59/82

ST62T35B/E35B

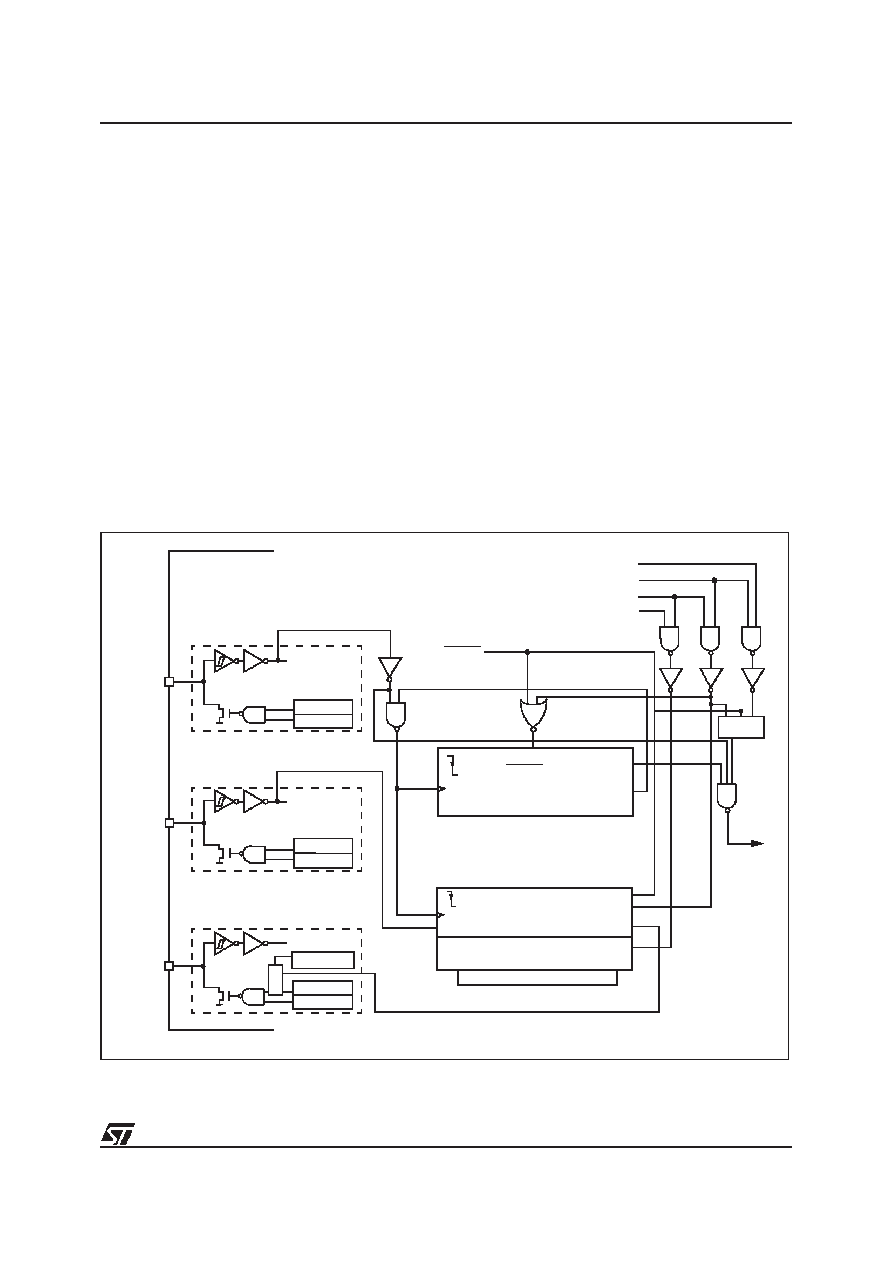

4.6 SERIAL PERIPHERAL INTERFACE (SPI)

The on-chip SPI is an optimized serial synchro-

nous interface that supports a wide range of in-

dustry standard SPI specifications. The on-chip

SPI is controlled by small and simple user soft-

ware to perform serial data exchange. The serial

shift clock can be implemented either by software

(using the bit-set and bit-reset instructions), with

the on-chip Timer 1 by externally connecting the

SPI clock pin to the timer pin or by directly apply-

ing an external clock to the Scl line.

The peripheral is composed by an 8-bit Data/shift

Register and a 4-bit binary counter while the Sin

pin is the serial shift input and Sout is the serial

shift output. These two lines can be tied together

to implement two wires protocols (I C-bus, etc).

When data is serialized, the MSB is the first bit.

Sin has to be programmed as input. For serial out-

put operation Sout has to be programmed as

open-drain output.

The SCL, Sin and Sout SPI clock and data signals

are connected to 3 I/O lines on the same external

pins. With these 3 lines, the SPI can operate in the

following operating modes: Software SPI, S-BUS,

I C-bus and as a standard serial I/O (clock, data,

enable). An interrupt request can be generated af-

ter eight clock pulses. Figure 35. shows the SPI

block diagram.

The SCL line clocks, on the falling edge, the shift

register and the counter. To allow SPI operation in

slave mode, the SCL pin must be programmed as

input and an external clock must be supplied to

this pin to drive the SPI peripheral.

In master mode, SCL is programmed as output, a

clock signal must be generated by software to set

and reset the port line.

Figure 35. SPI Block Diagram

Set Res

CLK

RESET

4-Bit Counter

(Q4=High after Clock8)

Data Reg

Direction

I/O Port

8-Bit Data

Shift Register

Reset

Load

DOUT

Output

Enable

8-Bit Tristate Data I/O

RESET

I/O Port

CP

DIN

D0............... .............D7

to Processor Data Bus

Q4

OPR Reg.

DIN

SCL

Sin

Sout

SPI Interrupt Disable Register

SPI Data Register

Data Reg

Direction

Data Reg

Direction

DOUT

Write

Read

MU

X 0

1

Interrupt

VR01504

58

相关PDF资料 |

PDF描述 |

|---|---|

| ST6235BQ1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| ST62P45BQ6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| ST62T03CM6E | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST62T10BM6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST62T25BB6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62P52C | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MOMTR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MPITR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MSATR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CN6/MMMTR | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。