- 您现在的位置:买卖IC网 > PDF目录98146 > ST7PLU09MCTRE (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 PDF资料下载

参数资料

| 型号: | ST7PLU09MCTRE |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 |

| 封装: | 0.150 INCH, ROHS COMPLIANT, PLASTIC, SOP-8 |

| 文件页数: | 111/124页 |

| 文件大小: | 1995K |

| 代理商: | ST7PLU09MCTRE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页当前第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页

ST7LUS5, ST7LU05, ST7LU09

Instruction set

87/124

Using a prebyte

The instructions are described with 1 to 4 bytes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three

different prebyte opcodes are defined. These prebytes modify the meaning of the instruction

they precede.

The whole instruction becomes:

PC-2

End of previous instruction

PC-1

Prebyte

PC

Opcode

PC+1

Additional word (0 to 2) according to the number of bytes required to compute

the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be

implemented. They precede the opcode of the instruction in X or the instruction using direct

addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent

addressing mode by a Y one.

PIX 92

Replace an instruction using direct, direct bit or direct relative addressing

mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an

instruction using indirect X indexed addressing mode.

PIY 91

Replace an instruction using X indirect indexed addressing mode by a Y one.

11.2.1

Illegal opcode reset

In order to provide enhanced robustness to the device against unexpected behavior, a

system of illegal opcode detection is implemented. If a code to be executed does not

correspond to any opcode or prebyte value, a reset is generated. This, combined with the

Watchdog, allows the detection and recovery from an unexpected fault or interference.

Note:

A valid prebyte associated with a valid opcode forming an unauthorized combination does

not generate a reset.

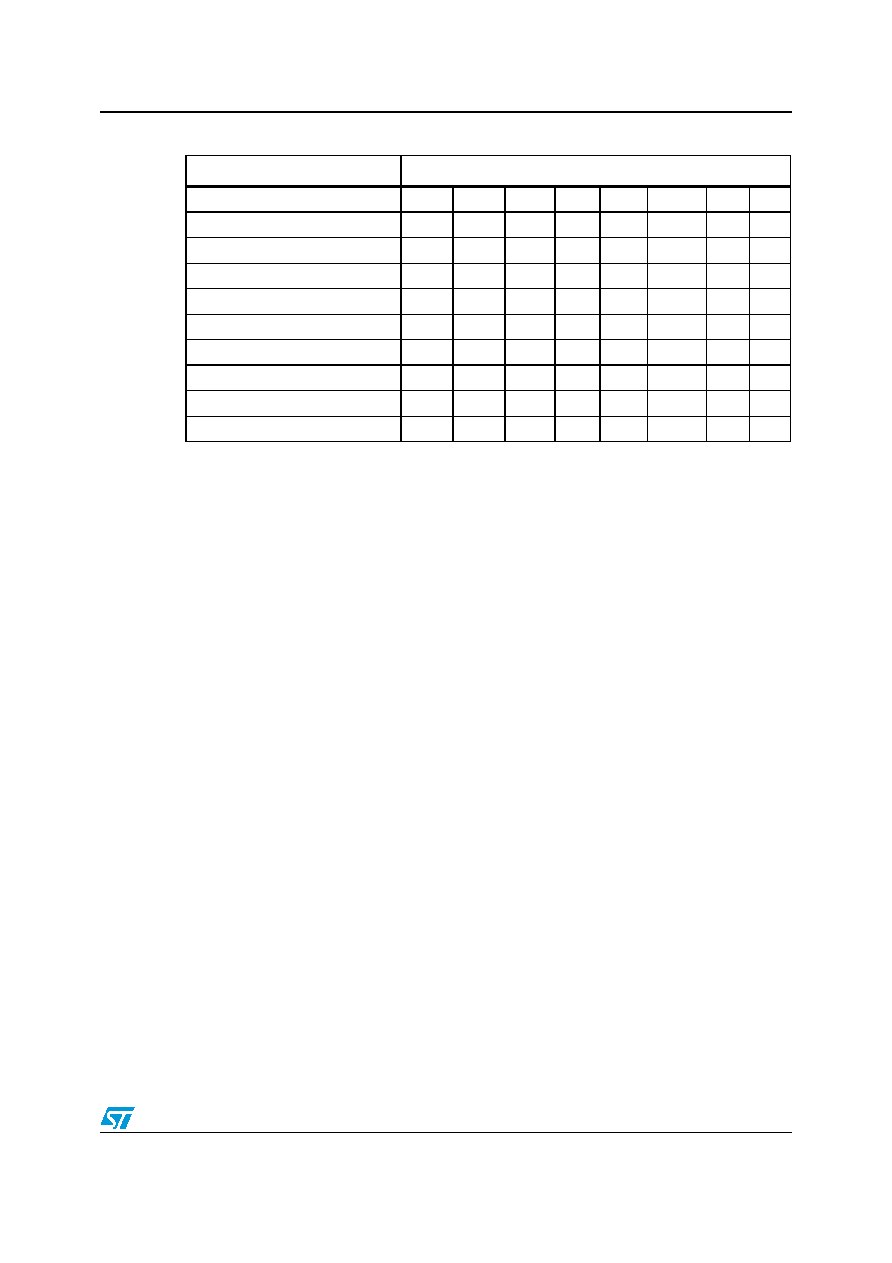

Compare and Tests

CP

TNZ

BCP

Logical operations

AND

OR

XOR

CPL

NEG

Bit Operation

BSET

BRES

Conditional Bit Test and Branch

BTJT

BTJF

Arithmetic operations

ADC

ADD

SUB

SBC

MUL

Shift and Rotates

SLL

SRL

SRA

RLC

RRC

SWAP

SLA

Unconditional Jump or Call

JRA

JRT

JRF

JP

CALL

CALLR

NOP

RET

Conditional Branch

JRxx

Interruption management

TRAP

WFI

HALT

IRET

Condition Code Flag modification

SIM

RIM

SCF

RCF

Table 59.

Instruction groups (continued)

Group

Instructions

相关PDF资料 |

PDF描述 |

|---|---|

| ST7PLU05MAE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 |

| ST7PLU09MAE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 |

| ST90135M5T6 | 16-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP80 |

| ST90T158M9Q6 | 16-BIT, OTPROM, 24 MHz, MICROCONTROLLER, PQFP80 |

| ST90158M9Q6 | 16-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7PMC1K2B3 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with nested interrupts, Flash, 10-bit ADC, brushless motor control, five timers, SPI, LINSCI? |

| ST7PMC1K2B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH NESTED INTERRUPTS, FLASH, 10-BIT ADC, BRUSHLESS MOTOR CONTROL, FIVE TIMERS, SPI, LINSCI |

| ST7PMC1K2T3 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with nested interrupts, Flash, 10-bit ADC, brushless motor control, five timers, SPI, LINSCI? |

| ST7PMC1K2T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH NESTED INTERRUPTS, FLASH, 10-BIT ADC, BRUSHLESS MOTOR CONTROL, FIVE TIMERS, SPI, LINSCI |

| ST7PMC1K2T6/ST7PMC1K2 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH NESTED INTERRUPTS, FLASH, 10-BIT ADC, BRUSHLESS MOTOR CONTROL, FIVE TIMERS, SPI, LINSCI |

发布紧急采购,3分钟左右您将得到回复。