- 您现在的位置:买卖IC网 > PDF目录98146 > ST90158P9C6 (STMICROELECTRONICS) 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC84 PDF资料下载

参数资料

| 型号: | ST90158P9C6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC84 |

| 封装: | PLASTIC, LCC-84 |

| 文件页数: | 104/189页 |

| 文件大小: | 3326K |

| 代理商: | ST90158P9C6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页当前第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页

21/189

ST90158 - DEVICE ARCHITECTURE

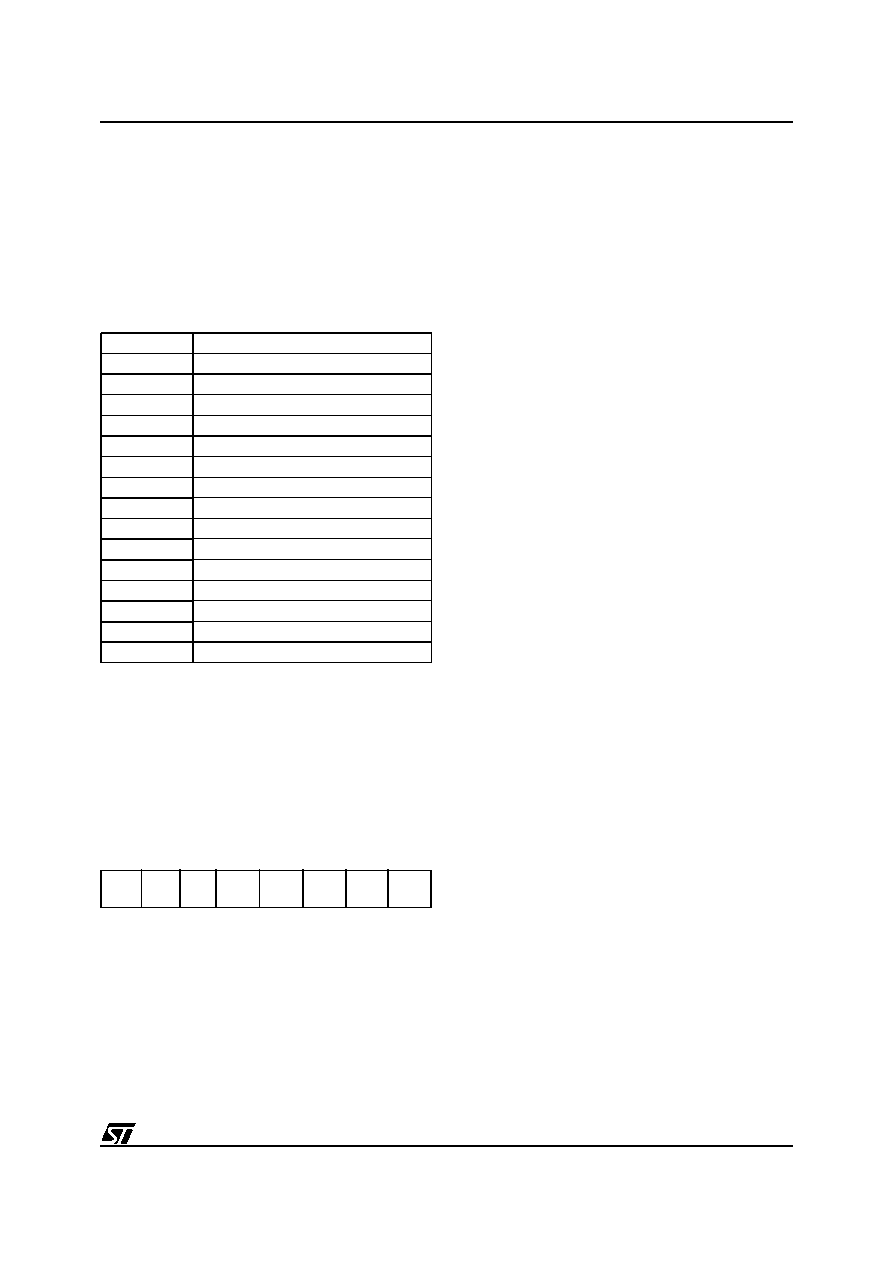

2.3 SYSTEM REGISTERS

The System registers are listed in Table 5 System

Registers (Group E). They are used to perform all

the important system settings. Their purpose is de-

scribed in the following pages. Refer to the chapter

dealing with I/O for a description of the PORT[5:0]

Data registers.

Table 5. System Registers (Group E)

2.3.1 Central Interrupt Control Register

Please refer to the ”INTERRUPT” and “DMA”

chapters for a detailed description of the ST9 inter-

rupt philosophy.

CENTRAL INTERRUPT CONTROL REGISTER

(CICR)

R230 - Read/Write

Register Group: E (System)

Reset Value: 1000 0111 (87h)

Bit 7 = GCEN:

Global Counter Enable.

This bit is the Global Counter Enable of the Multi-

function Timers. The GCEN bit is ANDed with the

CE bit in the TCR Register (only in devices featur-

ing the MFT Multifunction Timer) in order to enable

the Timers when both bits are set. This bit is set af-

ter the Reset cycle.

Note: If an MFT is not included in the ST9 device,

then this bit has no effect.

Bit 6 = TLIP:

Top Level Interrupt Pending.

This bit is set by hardware when a Top Level Inter-

rupt Request is recognized. This bit can also be

set by software to simulate a Top Level Interrupt

Request.

0: No Top Level Interrupt pending

1: Top Level Interrupt pending

Bit 5 = TLI:

Top Level Interrupt bit.

0: Top Level Interrupt is acknowledged depending

on the TLNM bit in the NICR Register.

1: Top Level Interrupt is acknowledged depending

on the IEN and TLNM bits in the NICR Register

(described in the Interrupt chapter).

Bit 4 = IEN:

Interrupt Enable .

This bit is cleared by interrupt acknowledgement,

and set by interrupt return (iret). IEN is modified

implicitly by iret, ei and di instructions or by an

interrupt acknowledge cycle. It can also be explic-

itly written by the user, but only when no interrupt

is pending. Therefore, the user should execute a

di

instruction (or guarantee by other means that

no interrupt request can arrive) before any write

operation to the CICR register.

0: Disable all interrupts except Top Level Interrupt.

1: Enable Interrupts

Bit 3 = IAM:

Interrupt Arbitration Mode.

This bit is set and cleared by software to select the

arbitration mode.

0: Concurrent Mode

1: Nested Mode.

Bit 2:0 = CPL[2:0]:

Current Priority Level.

These three bits record the priority level of the rou-

tine currently running (i.e. the Current Priority Lev-

el, CPL). The highest priority level is represented

by 000, and the lowest by 111. The CPL bits can

be set by hardware or software and provide the

reference according to which subsequent inter-

rupts are either left pending or are allowed to inter-

rupt the current interrupt service routine. When the

current interrupt is replaced by one of a higher pri-

ority, the current priority value is automatically

stored until required in the NICR register.

R239 (EFh)

SSPLR

R238 (EEh)

SSPHR

R237 (EDh)

USPLR

R236 (ECh)

USPHR

R235 (EBh)

MODE REGISTER

R234 (EAh)

PAGE POINTER REGISTER

R233 (E9h)

REGISTER POINTER 1

R232 (E8h)

REGISTER POINTER 0

R231 (E7h)

FLAG REGISTER

R230 (E6h)

CENTRAL INT. CNTL REG

R229 (E5h)

PORT5 DATA REG.

R228 (E4h)

PORT4 DATA REG.

R227 (E3h)

PORT3 DATA REG.

R226 (E2h)

PORT2 DATA REG.

R225 (E1h)

PORT1 DATA REG.

R224 (E0h)

PORT0 DATA REG.

70

GCE

N

TLIP

TLI

IEN

IAM

CPL2 CPL1 CPL0

9

相关PDF资料 |

PDF描述 |

|---|---|

| ST90E28L1/ES | 16-BIT, UVPROM, 24 MHz, MICROCONTROLLER, CQCC44 |

| ST90E30D1/ES | 16-BIT, UVPROM, 24 MHz, MICROCONTROLLER, CDIP56 |

| ST90E30L1/ES | 16-BIT, UVPROM, 24 MHz, MICROCONTROLLER, CQCC68 |

| ST90T30B6 | 16-BIT, OTPROM, 24 MHz, MICROCONTROLLER, PDIP56 |

| ST90R40C1 | 16-BIT, 24 MHz, MICROCONTROLLER, PQCC68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST90158-ST90135 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8/16-BIT MCU FAMILY WITH UP TO 64K ROM/OTP/EPROM AND UP TO 2K RAM |

| ST9016 | 制造商:SEMTECH_ELEC 制造商全称:SEMTECH ELECTRONICS LTD. 功能描述:NPN Silicon Epitaxial Planar Transistor |

| ST9018 | 制造商:SEMTECH_ELEC 制造商全称:SEMTECH ELECTRONICS LTD. 功能描述:NPN Silicon Epitaxial Planar Transistor |

| ST901T | 功能描述:达林顿晶体管 NPN Power Darlington RoHS:否 制造商:Texas Instruments 配置:Octal 晶体管极性:NPN 集电极—发射极最大电压 VCEO:50 V 发射极 - 基极电压 VEBO: 集电极—基极电压 VCBO: 最大直流电集电极电流:0.5 A 最大集电极截止电流: 功率耗散: 最大工作温度:+ 150 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-18 封装:Reel |

| ST901T_05 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:HIGH VOLTAGE IGNITION COIL DRIVER NPN POWER TRANSISTOR |

发布紧急采购,3分钟左右您将得到回复。