- 您现在的位置:买卖IC网 > PDF目录380730 > ST92163N4G0V (意法半导体) 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT PDF资料下载

参数资料

| 型号: | ST92163N4G0V |

| 厂商: | 意法半导体 |

| 英文描述: | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| 中文描述: | 16位产品全速USB微控制器16端点,20,000光盘和2K的RAM,I2C和脊髓损伤的复合设备, |

| 文件页数: | 48/224页 |

| 文件大小: | 1372K |

| 代理商: | ST92163N4G0V |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页

48/224

ST92163 - INTERRUPTS

INTERRUPTS

(Cont’d)

3.2.2

Segment

Routines

The ENCSR bit in the EMR2 register can be used

to select between original ST9 backward compati-

bility mode and ST9+ interrupt management

mode.

Paging

During

Interrupt

ST9 backward compatibility mode(ENCSR =0)

If ENCSR is reset, the CPU works in original ST9

compatibility mode. For the duration of the inter-

rupt service routine, ISR is used instead of CSR,

and the interrupt stack frame is identical to that of

the original ST9: only the PC and Flags are

pushed.

This avoids saving the CSR on the stack in the

event of an interrupt, thus ensuring a faster inter-

rupt response time.

It is not possible for an interrupt service routine to

perform inter-segment calls or jumps: these in-

structions would update the CSR, which, in this

case, is not used (ISR is used instead). The code

segment size for all interrupt service routines is

thus limited to 64K bytes.

ST9+ mode (ENCSR = 1)

If ENCSR is set, ISR is only used to point to the in-

terrupt vector table and to initialize the CSR at the

beginning of the interrupt service routine: the old

CSR ispushed onto the stack together with the PC

and flags, and CSR is then loaded with the con-

tents of ISR.

In this case,

iret

will also restore CSR from the

stack. This approach allows interrupt service rou-

tines to access the entire 4 Mbytes of address

space. The drawback is that the interrupt response

time is slightly increased, because of the need to

also save CSR on the stack.

Full compatibilitywith the original ST9 is lost in this

case, because the interrupt stack frame is differ-

ent.

3.3 INTERRUPT PRIORITY LEVELS

The ST9 supports a fully programmable interrupt

priority structure. Nine priority levels are available

to define the channel priority relationships:

– The on-chip peripheralchannels and the eight

external interrupt sources can be programmed

within eight priority levels. Each channel has a 3-

bit field, PRL (Priority Level), that defines its pri-

ority level in the range from 0 (highest priority) to

7 (lowest priority).

– The 9th level (Top Level Priority) is reserved for

the Timer/Watchdog or the External Pseudo

Non-Maskable Interrupt. An Interrupt service

routine at this level cannot be interrupted in any

arbitration mode. Its mask canbe both maskable

(TLI) or non-maskable (TLNM).

3.4 PRIORITY LEVEL ARBITRATION

The 3 bits of CPL (Current Priority Level) in the

Central Interrupt Control Register contain the pri-

ority of the currently running program (CPU priori-

ty). CPL is set to 7 (lowest priority) upon reset and

can be modified during program execution either

by software or automatically by hardware accord-

ing to the selected Arbitration Mode.

During every instruction, an arbitration phase

takes place, during which,for every channel capa-

ble of generating an Interrupt, each priority level is

compared to all the other requests (interrupts or

DMA).

If the highest priority request is an interrupt, its

PRL value must be strictly lower (that is, higher pri-

ority) thanthe CPL value stored in the CICR regis-

ter (R230) in order to be acknowledged. The Top

Level Interrupt overrides every other priority.

3.4.1 Priority level 7 (Lowest)

Interrupt requests at PRL level 7 cannot be ac-

knowledged, as this PRL value (the lowest possi-

ble priority) cannot be strictly lower than the CPL

value. This can be of use in a fully polled interrupt

environment.

3.4.2 Maximum depth of nesting

No more than 8 routinescan be nested. If an inter-

rupt routine at level N is being serviced, no other

Interrupts located at level N can interrupt it. This

guarantees a maximum numberof 8 nested levels

including the Top Level Interrupt request.

3.4.3 Simultaneous Interrupts

If two or more requests occur at the sametime and

at the same priority level, an on-chip daisy chain,

specific to every ST9 version, selects the channel

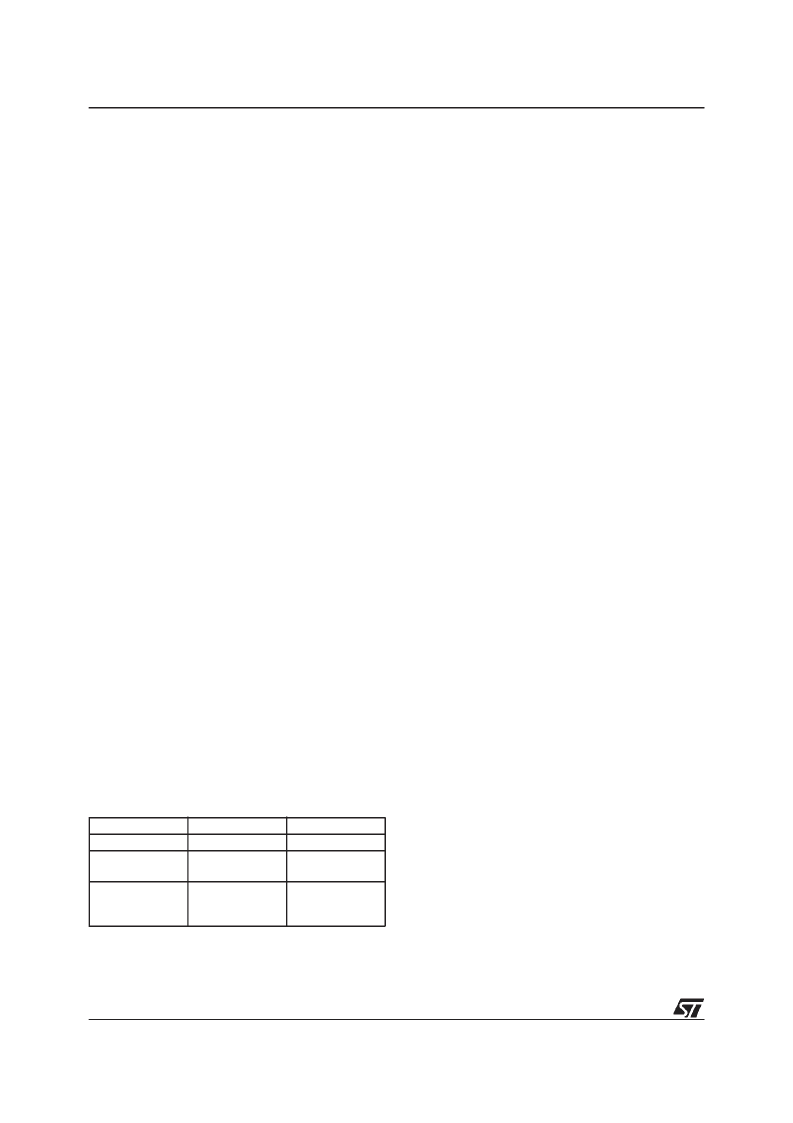

ENCSR Bit

Mode

Pushed/Popped

Registers

Max. Code Size

for interrupt

service routine

0

1

ST9 Compatible

ST9+

PC, FLAGR

PC, FLAGR,

CSR

64KB

Within 1segment

<4 MB

Across segments

相关PDF资料 |

PDF描述 |

|---|---|

| ST92163R4G0V | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163R4T1V | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92E163R4T1V | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92T163R4T1V | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163R4B0 | 8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST92163N4G1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4G1E | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4G1L | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163N4G1V | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS, 20K ROM, 2K RAM, I2C, SCI, & MFT |

| ST92163R4 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8/16-BIT FULL SPEED USB MCU FOR COMPOSITE DEVICES WITH 16 ENDPOINTS. 20K ROM. 2K RAM. I 2 C. SCI. & MFT |

发布紧急采购,3分钟左右您将得到回复。