参数资料

| 型号: | SY87739LHG |

| 厂商: | Micrel Inc |

| 文件页数: | 17/17页 |

| 文件大小: | 0K |

| 描述: | IC SYNTHESIZER FRACT 3.3V 32TQFP |

| 标准包装: | 250 |

| 系列: | AnyClock® |

| 类型: | 分数合成器 |

| PLL: | 是 |

| 主要目的: | 以太网,光纤通道,SONET/SDH/ATM |

| 输入: | PECL |

| 输出: | PECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 729MHz |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP 裸露焊盘 |

| 供应商设备封装: | 32-EPAD-TQFP |

| 包装: | 托盘 |

| 其它名称: | 576-1407 |

Micrel, Inc.

SY87739L

June 2011

9

M9999-061511

hbwhelp@micrel.com

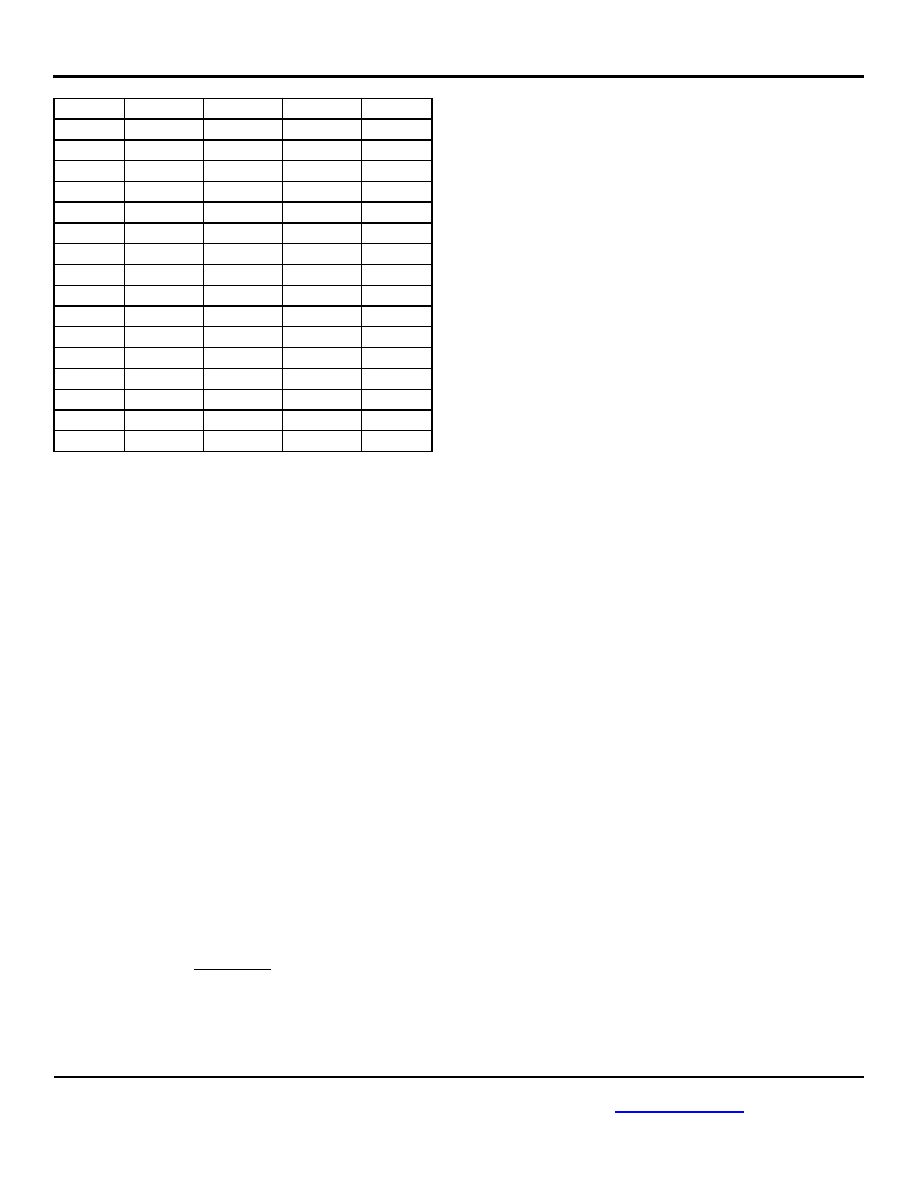

DivSel3

DivSel2

DivSel1

DivSel0

P

0

17

0

1

18

0

1

0

19

0

1

20

0

1

0

21

0

1

0

1

22

0

1

0

23

0

1

24

1

0

25

1

0

1

26

1

0

1

0

27

1

0

1

28

1

0

29

1

0

1

30

1

0

31

1

32

or (408) 955-1690

Table 1. DivSel Divider Setting

Fractional-N Control

This circuit controls the P/P–1 divider, selecting the

appropriate divide ratio, either P or P–1, in the correct

pattern.

As explained in the example of Figure 2 above,

controlling the P/P–1 divider amounts to generating a

repeating binary bit stream. In that example, a “1”

represents dividing by 4, and a “0” represents dividing by

3. The full cycle, “101”, says to divide by 4 twice, and to

divide by 3 once.

In the general case, the pattern “101” need not change

based on the P divider value. To multiply by 14/3 instead

of 11/3, for example, the same “101” pattern would be

used, but we would alternate dividing by 5 and 4, instead

of dividing by 4 and 3. The P value, in effect, represents

the integer part of the multiplication factor.

The repeating binary bit pattern really depends only on

the number of times to divide by P, and the number of

times to divide by P–1. We label the number of times to

divide by P as QP, and the number of times to divide by

P–1 as QP–1. The fractional-N synthesizer generates its

output frequency as per this formula:

fFNOUT =

+

1

P

1

P

Q

P

× f

REF

In Figure 2, we multiply by 11/3, or 41/3. Matching

against the formula, P = 4, QP–1 = 1, and QP =2.

The SY87739L accepts QP and QP–1 values from its

MicroWire interface, where they exist as the 5-bit

values “qp” and “qpm1.” Both values are unsigned binary

numbers. QP and QP-1 are both constrained to be 31 or

less, and their sum is also constrained to be 31 or less.

That means that the denominator in the above formula

must be 31 or less.

As would be expected from the formula, setting QP to

zero causes frequency multiplication exactly by P–1.

Setting QP–1 to zero causes frequency multiplication

exactly by P. The SY87739L behavior is undefined if

both QP and QP–1 are both set to zero.

In the general case, the length of the repeating binary bit

pattern is QP + QP–1. It consists of QP “1”, and QP–1 “0.”

The SY87739L accomplishes this by implementing

Bresenham’s algorithm in hardware. To see how this

works, we need a more complicated example. Let’s say

we need to multiply by 110/23, or 5 – 5/23. In this

example, P = 5, QP–1 = 5, and QP = 18. The nave

approach would generate a bit pattern of:

11111 11111 11111 11100 000

The spaces between groups of five digits are added for

readability only. This pattern is 23 bits long, with QP (that

is, 18) “1” and QP–1 (that is, 5) “0”, so it will multiply

correctly, but it doesn’t match P/P–1 divider edges to

input edges in the best way possible.

In fact, the best pattern, in terms of minimizing distance

between divider and reference input edges, is:

11110 11110 1110 11110 1110

Table 2 shows how Bresenham’s algorithm works. The

first column is an accumulator. It starts at zero, but

otherwise takes the result from the fourth column of the

previous row. The second column is the value to add to

the accumulator at each step. In the general case, this is

always QP–1. The third column forms the sum. The fourth

column takes the sum modulo (QP + QP–1).

The last column is “0” whenever the modulo changes the

sum. Note that the Table has 23 rows, before the sum is

zero, and the entire algorithm repeats itself.

相关PDF资料 |

PDF描述 |

|---|---|

| SY87813LHG | IC CLOCK/DATA REC 1.3GBPS 32TQFP |

| SY89295UTI TR | IC DELAY LINE 1024TAP 32-TQFP |

| SY89296UTI TR | IC DELAY LINE 1024TAP 32-TQFP |

| SY89297UMH TR | IC DELAY LINE 1024TAP 2NS 24-MLF |

| SY897132LKY TR | IC LINK REPLICATOR 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY87739LHI | 功能描述:IC SYNTHESIZER FRACT 3.3V 32TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:AnyClock® 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| SY87739LHITR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROTOCOL TRANSPARENT 3.3V 10MHz to 729MHz FRACTIONAL-N SYNTHESIZER |

| SY87739LHY | 功能描述:时钟合成器/抖动清除器 3.3V Fractional N Synthesizer (10MHz to 729MHz) (Lead Free/I Temp/32 pin TQFP) RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| SY87739LHY TR | 功能描述:时钟合成器/抖动清除器 3.3V Fractional N Synthesizer (10MHz to 729MHz) (Lead Free/I Temp/32 pin TQFP) RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| SY87739LHYTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROTOCOL TRANSPARENT 3.3V 10MHz to 729MHz FRACTIONAL-N SYNTHESIZER |

发布紧急采购,3分钟左右您将得到回复。