- 您现在的位置:买卖IC网 > PDF目录361344 > T436416A-6SG (TM Technology, Inc.) 4M X 16 SDRAM PDF资料下载

参数资料

| 型号: | T436416A-6SG |

| 厂商: | TM Technology, Inc. |

| 英文描述: | 4M X 16 SDRAM |

| 中文描述: | 4米× 16内存 |

| 文件页数: | 25/29页 |

| 文件大小: | 712K |

| 代理商: | T436416A-6SG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页

TE

CH

tm

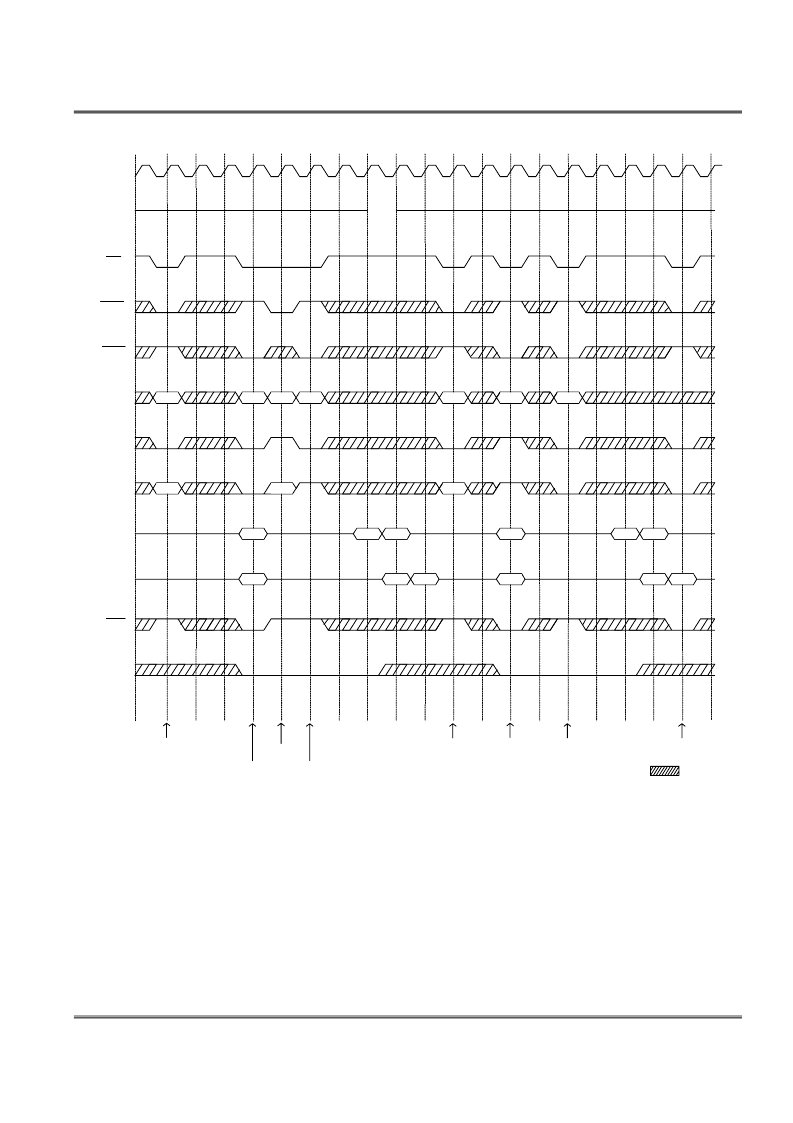

Burst Read Single bit Write Cycle @ Burst Length = 2

0

1

2

3

4

T436416A

TM Technology Inc. reserves the right

P.25

to change products or specifications without notice.

Publication Date: MAY. 2003

Revision: B

C L O C K

C K E

C S

R A S

C A S

A D D R

B A

A 1 0 /A P

C L = 2

C L = 3

W E

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

H IG H

D Q M

D Q

:D o n 't c a re

* N o te2

R A a

C A a

R B b

C A b

R A c

C B c

C A d

R A a

R B b

R A c

D A a0

D A a0

D A b 0

D A b 0

D A b 1

D A b 1

D B c0

D B c0

D A d 0

D A d 1

D A d 0

D A d 1

R o w A c tiv e

(A -B a n k )

W rite (A -

B an k )

R o w A c tiv e

(A -B a n k )

R ead w ith A u to

P rech arg e (A -

B an k )

R o w A c tiv e

(A -B a n k )

W rite w ith A u to

P rech arg e (A -

B an k )

R ead (A -

B an k )

P rech arg e

(A -B a n k )

*Note : 1. BRSW modes is enabled by setting A

9

‘High’ at MRS (Mode Register Set).

At the BRSW Mode, the burst length at write is fixed to ‘1’ regardless of programmed burst length.

2. When BRSW write command with auto precharge is executed, keep it in mind that

t

RAS

should not

be violated.

Auto precharge is executed at the next cycle of burst-end, so in the case of BRSW write command,

the precharge command will be issued after two clock cycle.

相关PDF资料 |

PDF描述 |

|---|---|

| T436416A-7.5S | 4M X 16 SDRAM |

| T436416A-7.5SG | 4M X 16 SDRAM |

| T436416A-7S | TERMINAL BLOCK END BARRIER IEC +OPTIONS |

| T436416A-7SG | 4M X 16 SDRAM |

| T436416A-8S | 4M X 16 SDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| T436416A-7.5S | 制造商:TMT 制造商全称:TMT 功能描述:4M X 16 SDRAM |

| T436416A-7.5SG | 制造商:TMT 制造商全称:TMT 功能描述:4M X 16 SDRAM |

| T436416A-7S | 制造商:TMT 制造商全称:TMT 功能描述:4M X 16 SDRAM |

| T436416A-7SG | 制造商:TMT 制造商全称:TMT 功能描述:4M X 16 SDRAM |

| T436416A-8S | 制造商:TMT 制造商全称:TMT 功能描述:4M X 16 SDRAM |

发布紧急采购,3分钟左右您将得到回复。