- 您现在的位置:买卖IC网 > PDF目录98217 > THS10082IDAG4 (TEXAS INSTRUMENTS INC) 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF资料下载

参数资料

| 型号: | THS10082IDAG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封装: | GREEN, PLASTIC, TSSOP-32 |

| 文件页数: | 13/37页 |

| 文件大小: | 350K |

| 代理商: | THS10082IDAG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

THS10082

SLAS254B MAY 2002 REVISED NOVEMBER 2002

www.ti.com

20

READING DATA FROM THE FIFO

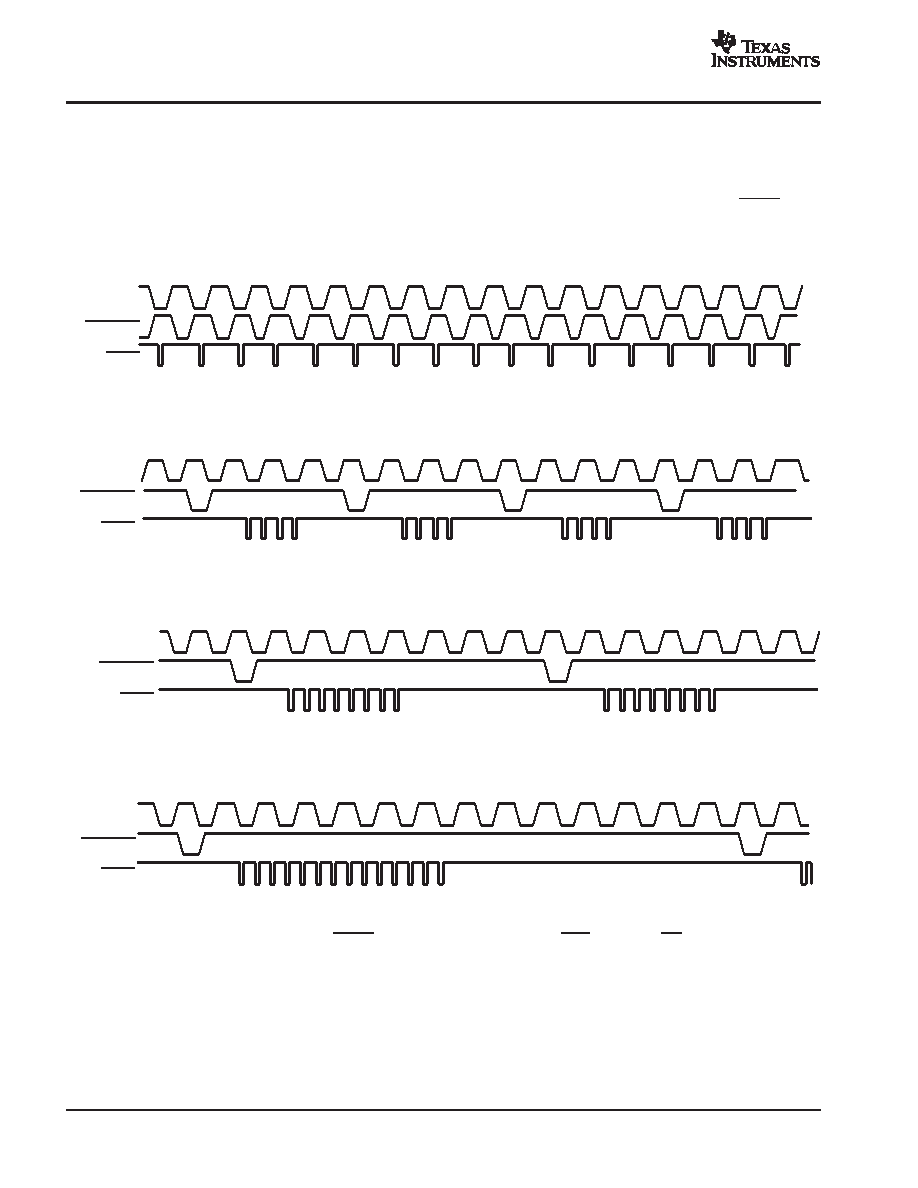

The THS10082 informs the connected processor via the digital output DATA_AV (data available) that a block of conversion

values is ready to be read. The block size to be read is always equal to the setting of the trigger level. The selectable trigger

levels depend on the number of selected analog input channels. For example, when choosing one analog input, a trigger

level of 1, 4, 8, and 14 can be selected. The following figures demonstrate the principle of reading the data (the READ signal

is asynchronous to CONV_CLK).

In Figure 30, a trigger level of 1 is selected. The control signal DATA_AV is set to an active low pulse. This means that the

connected processor has the task to read 1 value from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 30. Trigger Level 1 Selected

In Figure 31, a trigger level of 4 is selected. The control signal DATA_AV is set to an active low pulse. This means that the

connected processor has the task to read 4 values from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 31. Trigger Level 4 Selected

In Figure 32, a trigger level of 8 is selected. The control signal DATA_AV is set to an active low pulse. This means that the

connected processor has the task to read 8 values from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 32. Trigger Level 8 Selected

In Figure 33, a trigger level of 14 is selected. The control signal DATA_AV is set to an active low pulse. This means that

the connected processor has the task to read 14 values from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 33. Trigger Level 14 Selected

As shown in Figure 30 through Figure 33, READ, is the logical combination of CS0, CS1, and RD.

相关PDF资料 |

PDF描述 |

|---|---|

| THS1009CDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009CDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAG4 | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| THS1009 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDA | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAG4 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAR | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDARG4 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

发布紧急采购,3分钟左右您将得到回复。