- 您现在的位置:买卖IC网 > PDF目录98217 > THS10082IDAG4 (TEXAS INSTRUMENTS INC) 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF资料下载

参数资料

| 型号: | THS10082IDAG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封装: | GREEN, PLASTIC, TSSOP-32 |

| 文件页数: | 18/37页 |

| 文件大小: | 350K |

| 代理商: | THS10082IDAG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

THS10082

SLAS254B MAY 2002 REVISED NOVEMBER 2002

www.ti.com

25

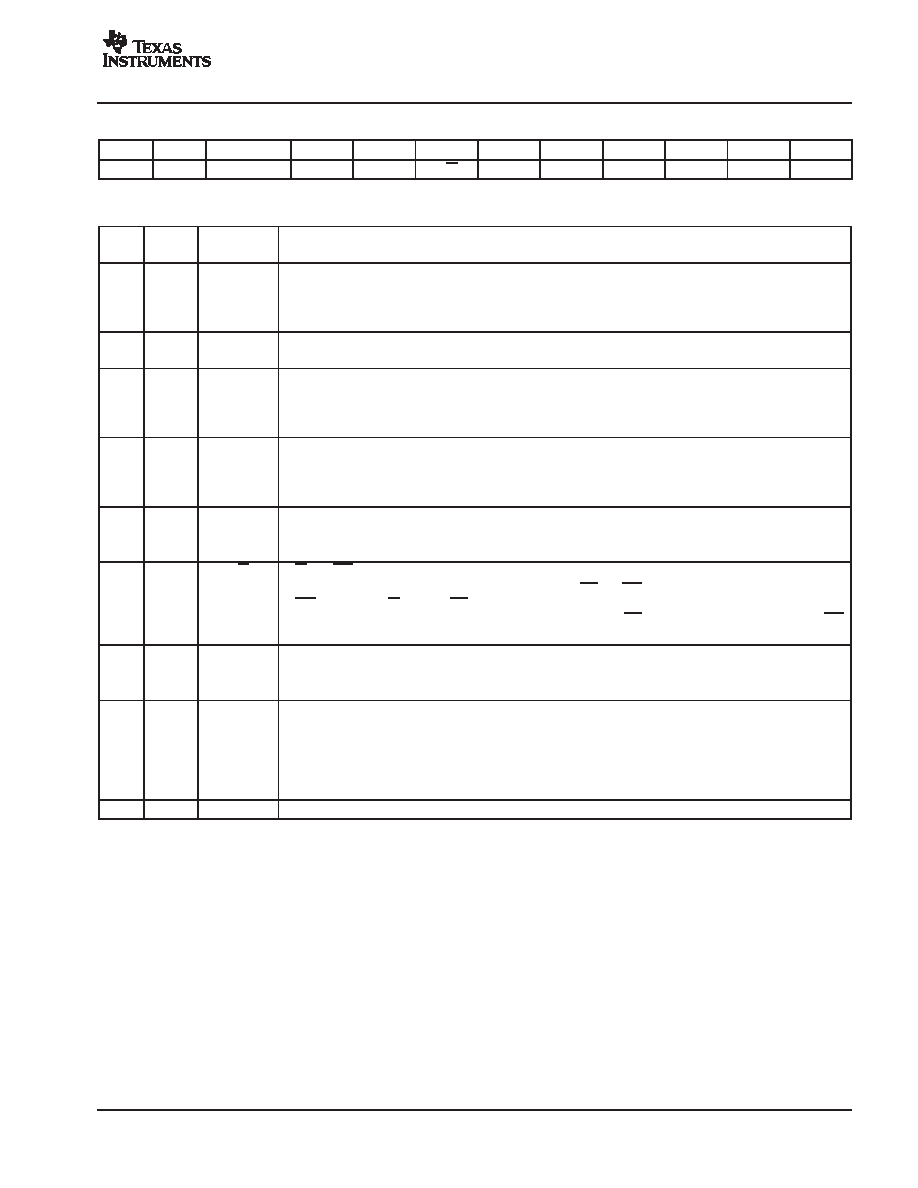

Control Register 1, Write Only (see Table 8)

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

1

RESERVED

OFFSET

BIN/2s

R/W

DATA_P

DATA_T

TRIG1

TRIG0

FRST

RESET

Table 12. Control Register 1 Bit Functions

BITS

RESET

VALUE

NAME

FUNCTION

0

RESET

Reset

Writing a 1 into this bit resets the device and sets the control register 0 and control register 1 to the reset values.

In addition the FIFO pointer and offset register is reset. After reset, it takes 5 clock cycles until the first value is

converted and written into the FIFO.

1

0

FRST

FRST: FIFO reset

By writing a 1 into this bit, the FIFO is reset.

2, 3

0,0

TRIG0,

TRIG1

FIFO trigger level

Bit 2 and bit 3 of control register 1 are used to set the trigger level for the FIFO. If the trigger level is reached, the

signal DATA_AV (data available) becomes active according to the settings of DATA_T and DATA_P. This

indicates to the processor that the ADC values can be read. Refer to Table 13.

4

1

DATA_T

DATA_AV type

Bit 4 of control register 1 controls whether the DATA_AV signal is a pulse or static (e.g., for edge or level

sensitive interrupt inputs). If it is set to 0, the DATA_AV signal is static. If it is set to 1, the DATA_AV signal is a

pulse. See Table 14.

5

1

DATA_P

DATA_AV polarity

Bit 5 of control register 1 controls the polarity of DATA_AV. If it is set to 1, DATA_AV is active high. If it is set to 0,

DATA_AV is active low. Refer to Table 14.

6

0

R/W

R/W, RD/WR selection

Bit 6 of control register 1 controls the function of the inputs RD and WR. When bit 6 in control register 1 is set to

1, WR becomes a R/W input and RD is disabled. From now on a read is signalled with R/W high and a write with

R/W as a low signal. If bit 6 in control register 1 is set to 0, the input RD becomes a read input and the input WR

becomes a write input.

7

0

BIN/2s

Complement select

If bit 7 of control register 1 is set to 0, the output value of the ADC is in twos complement. If bit 7 of

control register 1 is set to 1, the output value of the ADC is in binary format. Refer to Table 3 through Table 6.

8

0

OFFSET

Offset cancellation mode

Bit 8 = 0

→ normal conversion mode

Bit 8 = 1

→ offset calibration mode

If a 1 is written into bit 8 of control register 1, the device internally sets the inputs to zero and does a conver-

sion. The conversion result is stored in an offset register and subtracted from all conversions in order to

reduce the offset error.

9

0

RESERVED

Always write 0.

相关PDF资料 |

PDF描述 |

|---|---|

| THS1009CDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009CDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAG4 | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| THS1009 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDA | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAG4 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAR | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDARG4 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

发布紧急采购,3分钟左右您将得到回复。