- 您现在的位置:买卖IC网 > PDF目录98217 > THS10082IDAG4 (TEXAS INSTRUMENTS INC) 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF资料下载

参数资料

| 型号: | THS10082IDAG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封装: | GREEN, PLASTIC, TSSOP-32 |

| 文件页数: | 19/37页 |

| 文件大小: | 350K |

| 代理商: | THS10082IDAG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

THS10082

SLAS254B MAY 2002 REVISED NOVEMBER 2002

www.ti.com

26

FIFO TRIGGER LEVEL

Bit 2 and bit 3 (TRIG1, TRIG0) of control register 1 are used to set the trigger level of the FIFO (see Table 13). If the trigger

level is reached, the DATA_AV (data available) signal becomes active according to the setting of the signal DATA_AV to

indicate to the processor that the ADC values can be read.

Table 13 shows four different programmable trigger levels for each configuration. The FIFO trigger level, which can be

selected, is dependent on the number of input channels. One channel is considered as two inputs in differential

configuration, or one single-ended input. The processor, therefore, always reads the data from the FIFO in the same order

and is able to distinguish between the channels.

Table 13. FIFO Trigger Level

BIT 3

TRIG1

BIT 2

TRIG0

TRIGGER LEVEL

FOR 1 CHANNEL

(ADC values)

TRIGGER LEVEL

FOR 2 CHANNELS

(ADC values)

0

01

02

0

1

04

1

0

08

1

14

12

TIMING AND SIGNAL DESCRIPTION OF THE THS10082

The reading from the THS10082 and writing to the THS10082 is performed by using the chip select inputs (CS0, CS1),

the write input WR and the read input RD. The write input is configurable to a combined read/write input (R/W). This is

desired in cases where the connected processor consists of a combined read/write output signal (R/W). The two chip select

inputs can be used to interface easily to a processor.

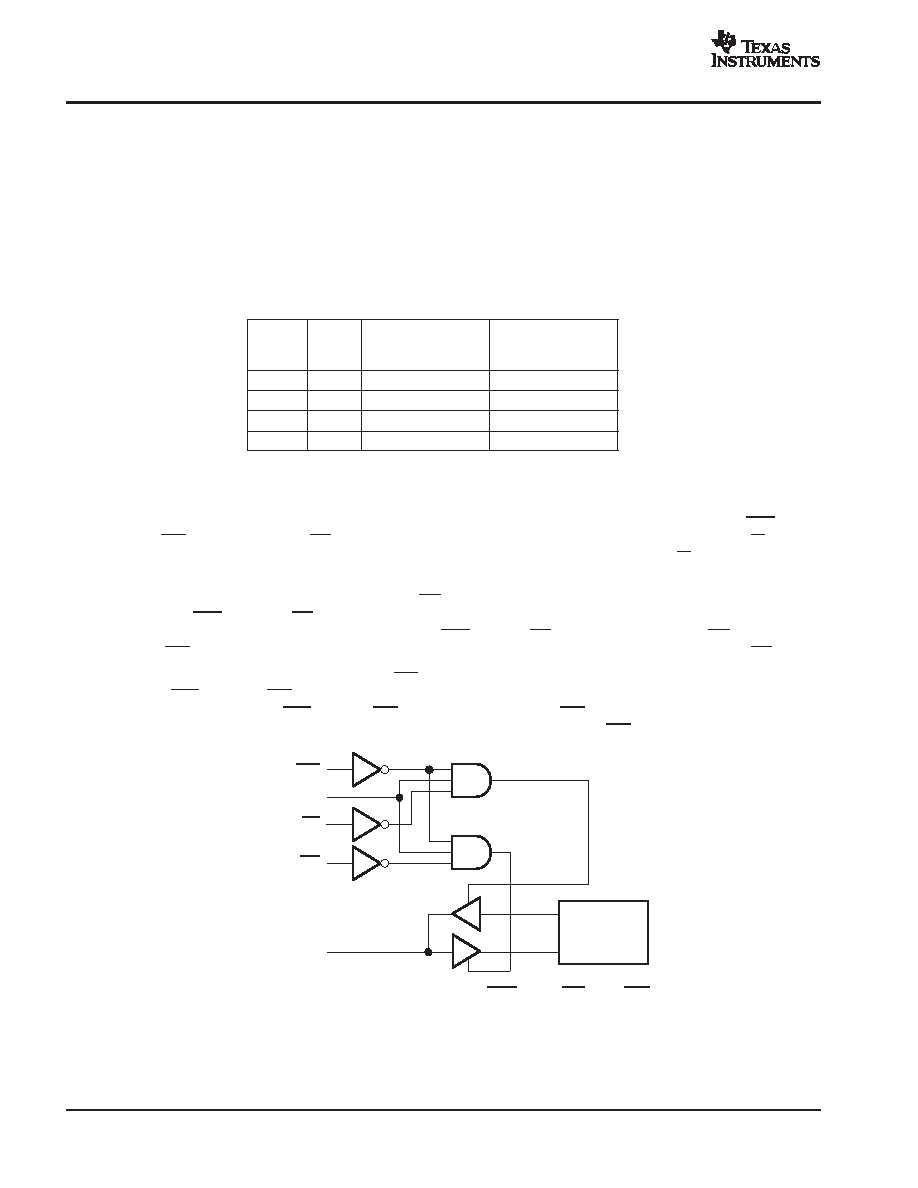

Reading from the THS10082 takes place by an internal RDint signal, which is generated from the logical combination of

the external signals CS0, CS1, and RD (see Figure 35). This signal is then used to strobe the words out of the FIFO and

to enable the output buffers. The last external signal (either CS0, CS1, or RD) to become valid makes RDint active while

the write input (WR) is inactive. The first of those external signals going to its inactive state then deactivates RDint.

Writing to the THS10082 takes place by an internal WRint signal, which is generated from the logical combination of the

external signals CS0, CS1 and WR. This signal is then used to strobe the control words into the control registers 0 and

1. The last external signal (either CS0, CS1, or WR) to become valid makes WRint active while the read input (RD) is

inactive. The first of those external signals going to its inactive state then deactivates WRint.

Read Enable

Write Enable

Control/Data

Registers

CS0

CS1

RD

WR

Data Bits

Figure 35. Logical Combination of CS0, CS1, RD, and WR

相关PDF资料 |

PDF描述 |

|---|---|

| THS1009CDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009CDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAG4 | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| THS1009 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDA | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAG4 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAR | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDARG4 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

发布紧急采购,3分钟左右您将得到回复。