- 您现在的位置:买卖IC网 > PDF目录382605 > TLC32047IFN (Texas Instruments, Inc.) Wide-Band Analog Interface Circuit PDF资料下载

参数资料

| 型号: | TLC32047IFN |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | Wide-Band Analog Interface Circuit |

| 中文描述: | 宽带模拟接口电路 |

| 文件页数: | 27/61页 |

| 文件大小: | 303K |

| 代理商: | TLC32047IFN |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

2–9

2.15.2

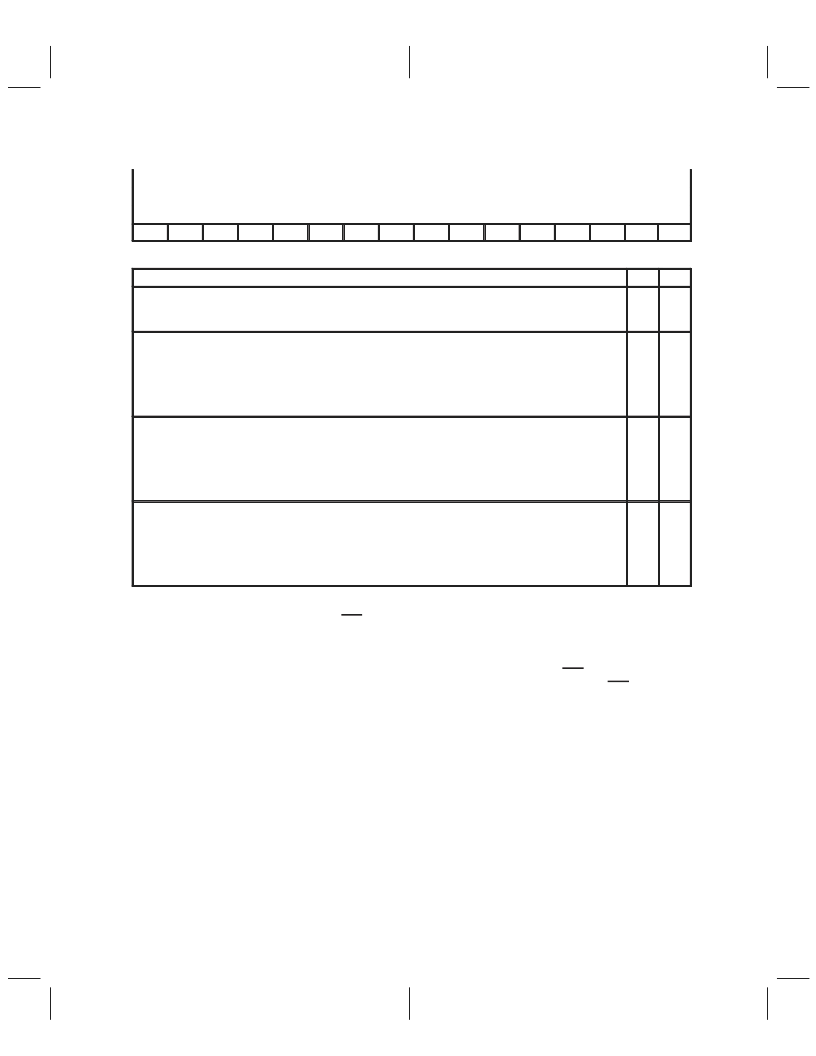

A/D OR D/A MSB

Primary DX Word Bit Pattern

1st bit sent

↓

D15

1st bit sent of 2nd byte

↓

D8

D7

A/D or D/A LSB

↓

D3

D2

D14

D13

D12

D11

D10

D9

D6

D5

D4

D1

D0

Table 2–2. Primary DX Serial Communication Protocol

FUNCTIONS

D1

D0

D15 (MSB)-D2

→

DAC Register.

TA

→

TX(A), RA

→

RX(A) (see Figure 2–1).

TB

→

TX(B), RB

→

RX(B) (see Figure 2–1).

D15 (MSB)-D2

→

DAC Register.

TA+TA

′

→

TX(A), RA+RA

′

→

RX(A) (see Figure 2–1).

TB

→

TX(B), RB

→

RX(B) (see Figure 2–1).

The next D/A and A/D conversion period is changed by the addition of TA

′

and RA

′

master clock cycles,

in which TA

′

and RA

′

can be positive, negative, or zero (refer to Table 2–4, AIC Responses to Improper

Conditions).

D15 (MSB)-D2

→

DAC Register.

TA–TA

′

→

TX(A), RA–RA

′

→

RX(A) (see Figure 2–1).

TB

→

TX(B), RB

→

RX(B) (see Figure 2–1).

The next D/A and A/D conversion period is changed by the subtraction of TA

′

and RA

′

master clock cycles,

in which TA

′

and RA

′

can be positive, negative, or zero (refer to Table 2–4, AIC Responses to Improper

Conditions).

D15 (MSB)-D2

→

DAC Register.

TA

→

TX(A), RA

→

RX(A) (see Figure 2–1).

TB

→

TX(B), RB

→

RX(B) (see Figure 2–1).

After a delay of four shift cycles, a secondary transmission follows to program the AIC to operate in the

desired configuration. In the telephone interface mode, data on DATA-DR is routed to DR (Serial Data

Output) during secondary transmission.

0

0

0

1

1

0

1

1

NOTE: Setting the two least significant bits to 1 in the normal transmission of DAC information (primary communications)

to the AIC initiates secondary communications upon completion of the primary communications. When the

primary communication is complete, FSX remains high for four shift clock cycles and then goes low and initiates

the secondary communication. The timing specifications for the primary and secondary communications are

identical. In this manner, the secondary communication, if initiated, is interleaved between successive primary

communications. This interleaving prevents the secondary communication from interfering with the primary

communications and DAC timing. This prevents the AIC from skipping a DAC output. FSR is not asserted during

secondary communications activity. However, in the dual-word (telephone interface) mode, FSD is asserted

during secondary communications but not during primary communications.

相关PDF资料 |

PDF描述 |

|---|---|

| TLC32047C | Wide-Band Analog Interface Circuit |

| TLC32047I | Wide-Band Analog Interface Circuit |

| TLC320A545C | SMA (F) TO BNC (M) ADAPTERS |

| TLC320A545C-I | SMA (F) TO MCX (F) ADAPTERS |

| TLC320A545I | SMA (F) TO MCX (M) ADAPTERS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLC32047IN | 制造商:TI 制造商全称:Texas Instruments 功能描述:Wide-Band Analog Interface Circuit |

| TLC3204CN | 制造商:Texas Instruments 功能描述: |

| TLC32071 | 制造商:TI 制造商全称:Texas Instruments 功能描述:HIGH-SPEED 8-BIT A/D AND D/A CONVERTER WITH 8-CHANNEL MULTIPLEXER |

| TLC320A545C | 制造商:TI 制造商全称:Texas Instruments 功能描述:Single Channel Data/Fax Codec |

| TLC320A545C-I | 制造商:TI 制造商全称:Texas Instruments 功能描述:Single Channel Data/Fax Codec |

发布紧急采购,3分钟左右您将得到回复。