- 您现在的位置:买卖IC网 > PDF目录98252 > TLV2556IPWR (TEXAS INSTRUMENTS INC) 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF资料下载

参数资料

| 型号: | TLV2556IPWR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封装: | GREEN, PLASTIC, TSSOP-20 |

| 文件页数: | 18/37页 |

| 文件大小: | 729K |

| 代理商: | TLV2556IPWR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

TLV2556

SLAS355A – DECEMBER 2001 – REVISED SEPTEMBER 2002

25

www.ti.com

PARAMETER MEASUREMENT INFORMATION

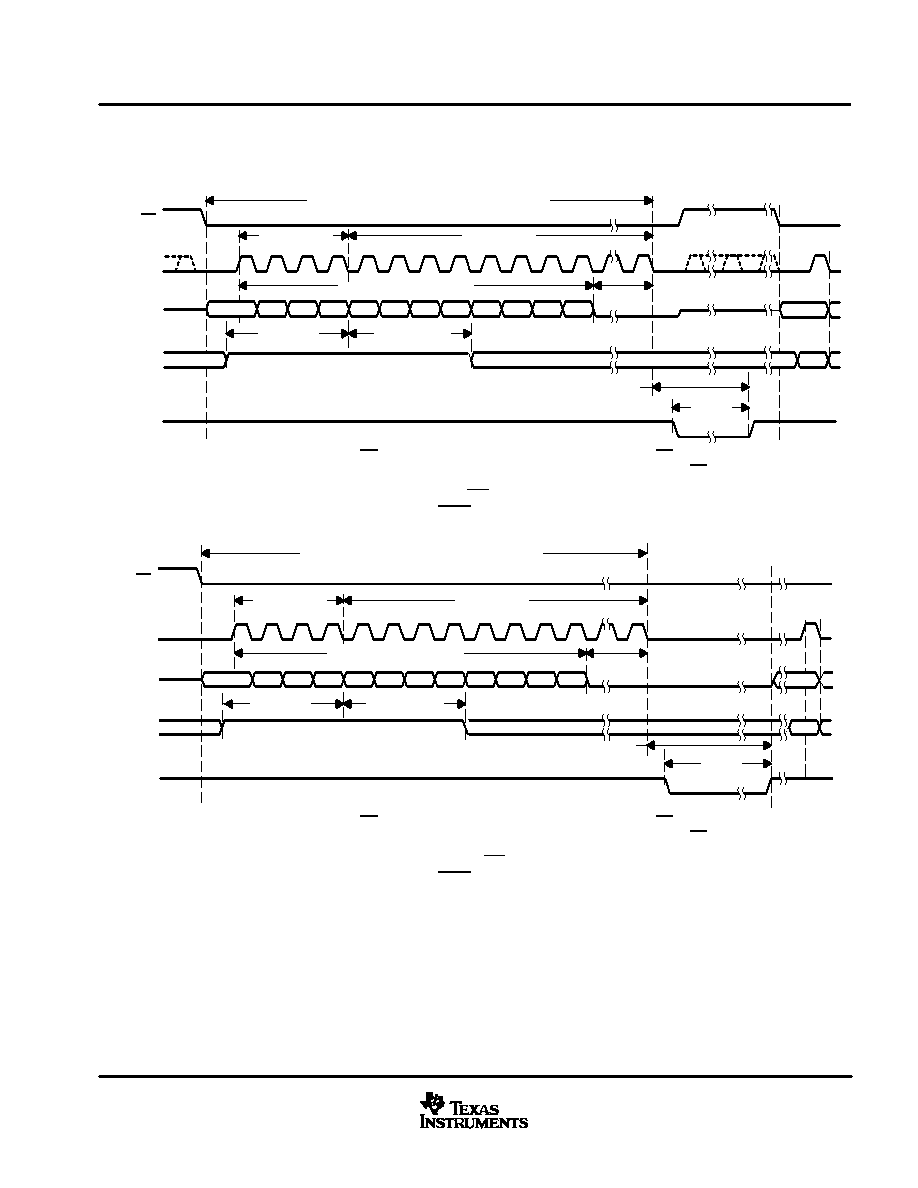

timing diagrams (continued)

DATA OUT

1

2

3

5

4

610

11

12

1

I/O CLOCK

MSB–1 MSB–2 MSB–3 MSB–4 MSB–5

MSB–8 MSB–9 LSB+1

LSB

Hi–Z State

DATA IN

8

7

9

MSB–6 MSB–7

D7

MSB

16

EOC

Initialize

Shift in New Multiplexer Address, Simultaneously

Shift Out Previous Conversion Result

Access Cycle

Sample Cycle

CS

Previous Conversion Data

Pad Zeros

Channel

Address

Output Data

Format

A/D Conversion Interval

tconv

DATA IN Can be Tied or Held High

NOTE A: To minimize errors caused by noise at CS, the internal circuitry waits for a setup time after the CS falling edge before responding to

control input signals. Therefore, no attempt should be made to clock in an address until the minimum CS setup time has elapsed.

Figure 52. Timing for Default Mode Using CS: (16-Clock Transfer, MSB First, Ext. Ref,

Pin 19 = EOC, Input = AIN0)

Access Cycle

Sample Cycle

MSB

DATA OUT

1

2

3

5

4

610

11

12

1

I/O CLOCK

MSB–1 MSB–2 MSB–3 MSB–4 MSB–5

MSB–8 MSB–9 LSB+1

LSB

16

DATA IN

8

7

9

MSB–6 MSB–7

Low Level

MSB

D7

EOC

Initialize

Shift in New Multiplexer Address, Simultaneously

Shift Out Previous Conversion Result

Previous Conversion Data

Pad Zeros

Channel

Address

Output Data

Format

A/D Conversion Interval

tconv

DATA IN Can be Tied or Held High

CS

NOTE A: To minimize errors caused by noise at CS, the internal circuitry waits for a setup time after the CS falling edge before responding to

control input signals. Therefore, no attempt should be made to clock in an address until the minimum CS setup time has elapsed.

Figure 53. Timing for Default Mode Not Using CS: (16-Clock Transfer, MSB First Ext. Ref,

Pin 19 = EOC, Input = AIN0)

To remove the device from default mode, CFGR2–D0 must be reset to 0. Valid sample/convert cycles can

resume on the cycle following the CFGR2 configuration.

相关PDF资料 |

PDF描述 |

|---|---|

| TLV2556IDW | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IPWG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556MPWREP | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556MPWREPG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV320ADC3001IYZHT | 2-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PBGA16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV2556IPWRG4 | 功能描述:模数转换器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2556MPWREP | 功能描述:模数转换器 - ADC EP 12B,200KSPS,11Ch Low Pwr,Serial ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2556MPWREPG4 | 功能描述:模数转换器 - ADC EP 12B,200KSPS,11Ch RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2620ID | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLV2620IDBVR | 功能描述:运算放大器 - 运放 800 uA/ch 11MHz RRO Lo-Vltg 1-Ch RoHS:否 制造商:STMicroelectronics 通道数量:4 共模抑制比(最小值):63 dB 输入补偿电压:1 mV 输入偏流(最大值):10 pA 工作电源电压:2.7 V to 5.5 V 安装风格:SMD/SMT 封装 / 箱体:QFN-16 转换速度:0.89 V/us 关闭:No 输出电流:55 mA 最大工作温度:+ 125 C 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。