- 您现在的位置:买卖IC网 > PDF目录382626 > TMX320F2812GHHS (Texas Instruments, Inc.) DIGITAL SIGNAL PROCESSORS PDF资料下载

参数资料

| 型号: | TMX320F2812GHHS |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 数字信号处理 |

| 英文描述: | DIGITAL SIGNAL PROCESSORS |

| 中文描述: | 数字信号处理器 |

| 文件页数: | 133/147页 |

| 文件大小: | 2021K |

| 代理商: | TMX320F2812GHHS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页当前第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页

Electrical Specifications

133

June 2004

SPRS257

6.29.7

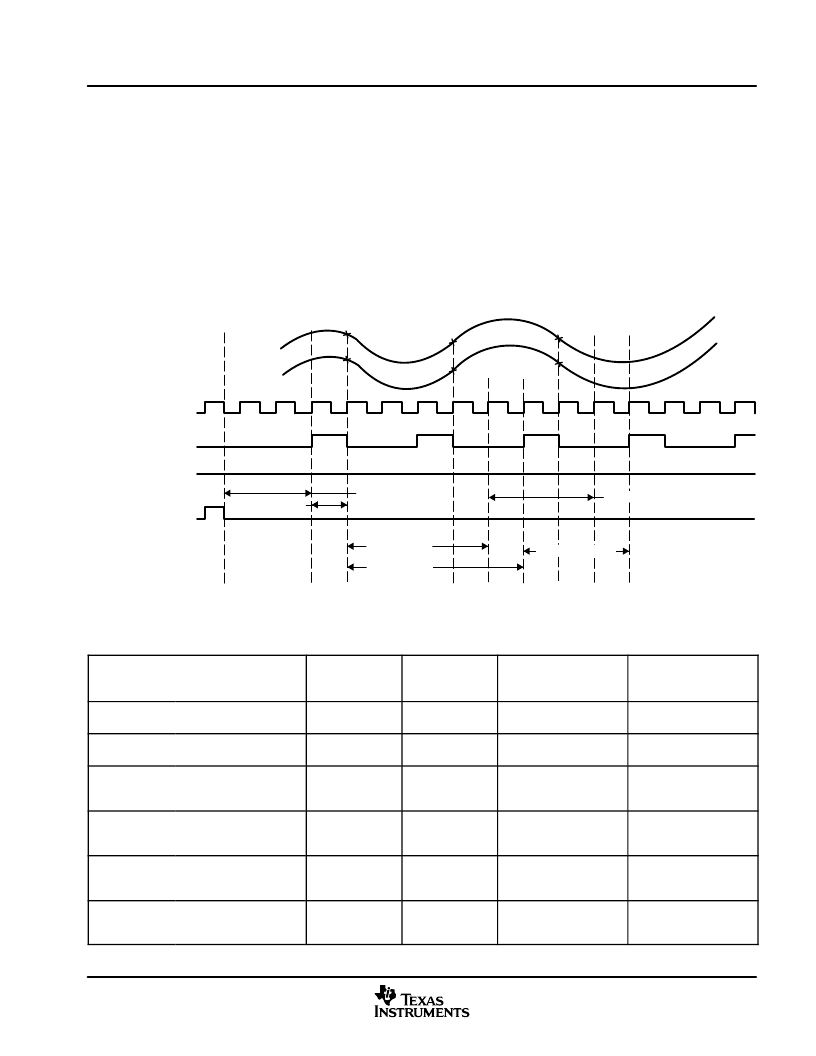

Simultaneous Sampling Mode (Dual-Channel) (SMODE = 1)

In simultaneous mode, the ADC can continuously convert input signals on any one pair of channels (A0/B0

to A7/B7). The ADC can start conversions on event triggers from the Event Managers (EVA/EVB), software

trigger, or from an external ADCSOC signal. If the SMODE bit is 1, the ADC will do conversions on two selected

channels on every Sample/Hold pulse. The conversion time and latency of the Result register update are

explained below. The ADC interrupt flags are set a few SYSCLKOUT cycles after the Result register update.

The selected channels will be sampled simultaneously at the falling edge of the Sample/Hold pulse. The

Sample/Hold pulse width can be programmed to be 1 ADC clock wide (minimum) or 16 ADC clocks wide

(maximum).

NOTE:

In Simultaneous mode, the ADCIN channel pair select has to be A0/B0, A1/B1, ...,

A7/B7, and

not

in other combinations (such as A1/B3, etc.).

Analog Input on

Channel Ax

Analog Input on

Channel Bv

ADC Clock

Sample and Hold

SH Pulse

t

SH

t

dschA0_n

t

dschB0_n

t

dschB0_n+1

Sample n

Sample n+1

Sample n+2

t

dschA0_n+1

t

d(SH)

ADC Event Trigger

from EV or Other

Sources

SMODE Bit

Figure 6

37. Simultaneous Sampling Mode Timing

Table 6

42. Simultaneous Sampling Mode Timing

SAMPLE n

SAMPLE n + 1

AT 25-MHz ADC

CLOCK,

t

c(ADCCLK)

= 40 ns

REMARKS

t

d(SH)

Delay time from event

trigger to sampling

2.5t

c(ADCCLK)

t

SH

Sample/Hold width/

Acquisition Width

(1 + Acqps) *

t

c(ADCCLK)

40 ns with Acqps = 0

Acqps value = 0-15

ADCTRL1[8:11]

t

d(schA0_n)

Delay time for first result

to appear in Result

register

4t

c(ADCCLK)

160 ns

t

d(schB0_n)

Delay time for first result

to appear in Result

register

5t

c(ADCCLK)

200 ns

t

d(schA0_n+1)

Delay time for

successive results to

appear in Result register

(3 + Acqps) *

t

c(ADCCLK)

120 ns

t

d(schB0_n+1)

Delay time for

successive results to

appear in Result register

(3 + Acqps) *

t

c(ADCCLK)

120 ns

A

相关PDF资料 |

PDF描述 |

|---|---|

| TMX320F2812PGFS | DIGITAL SIGNAL PROCESSORS |

| TMX320C2811GHHA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320C2811GHHQ | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320C2811GHHS | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320C2811PBKA | TMS320R2811, TMS320R2812 Digital Signal Processors |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMX320F2812PBKA | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320F2812PBKQ | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320F2812PBKS | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMX320F2812PGFA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TMX320F2812PGFMEP | 制造商:TI 制造商全称:Texas Instruments 功能描述:Digital Signal Processors |

发布紧急采购,3分钟左右您将得到回复。