- 您现在的位置:买卖IC网 > PDF目录382630 > TMX320F2812ZHHS (Texas Instruments, Inc.) TMS320R2811, TMS320R2812 Digital Signal Processors PDF资料下载

参数资料

| 型号: | TMX320F2812ZHHS |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 数字信号处理 |

| 英文描述: | TMS320R2811, TMS320R2812 Digital Signal Processors |

| 中文描述: | TMS320R2811,TMS320R2812数字信号处理器 |

| 文件页数: | 121/147页 |

| 文件大小: | 2021K |

| 代理商: | TMX320F2812ZHHS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页当前第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页

Electrical Specifications

121

June 2004

SPRS257

6.26

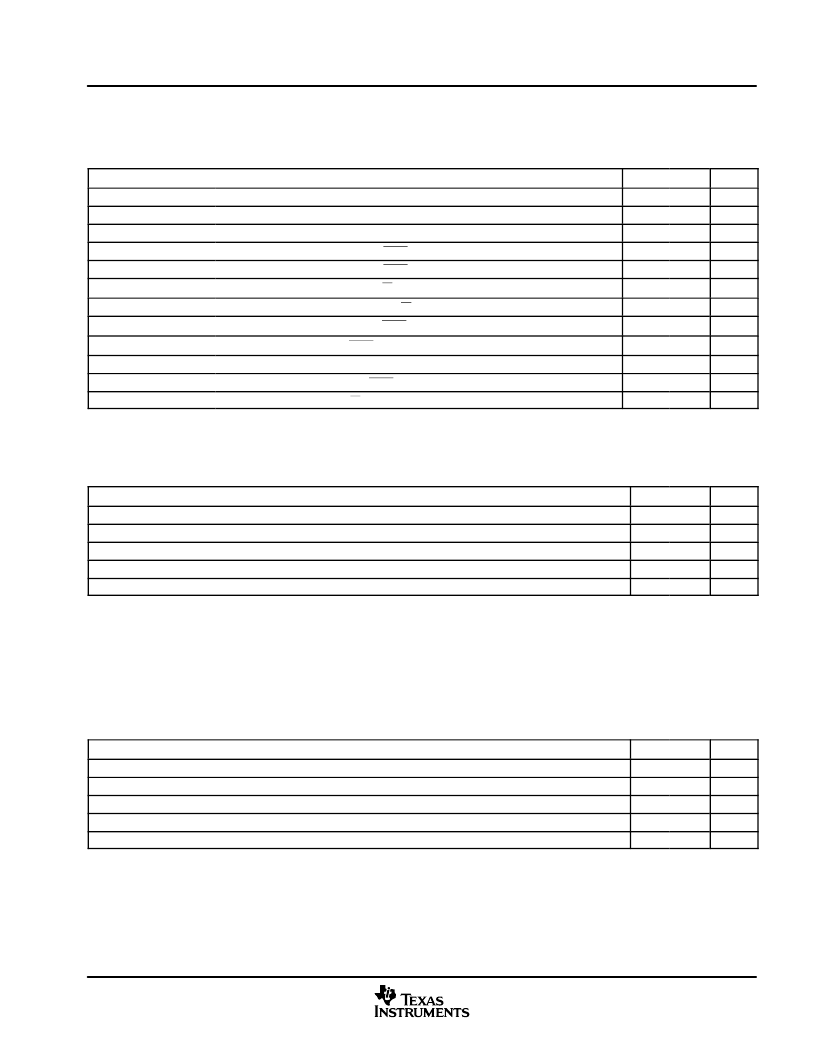

External Interface Ready-on-Write Timing With One External Wait State

Table 6

33. External Memory Interface Write Switching Characteristics

(Ready-on-Write, 1 Wait State)

PARAMETER

MIN

MAX

UNIT

t

d(XCOH-XZCSL)

t

d(XCOHL-XZCSH)

t

d(XCOH-XA)

t

d(XCOHL-XWEL)

t

d(XCOHL-XWEH)

t

d(XCOH-XRNWL)

t

d(XCOHL-XRNWH)

t

en(XD)XWEL

t

d(XWEL-XD)

t

h(XA)XZCSH

t

h(XD)XWE

t

dis(XD)XRNW

During inactive cycles, the XINTF address bus will always hold the last address put out on the bus. This includes alignment cycles.

TW = trail period, write access (see Table 6

24)

Delay time, XCLKOUT high to zone chip-select active low

Delay time, XCLKOUT high or low to zone chip-select inactive high

Delay time, XCLKOUT high to address valid

Delay time, XCLKOUT high/low to XWE low

Delay time, XCLKOUT high/low to XWE high

Delay time, XCLKOUT high to XR/W low

1

3

2

2

2

1

ns

ns

ns

ns

ns

ns

2

Delay time, XCLKOUT high/low to XR/W high

Enable time, data bus driven from XWE low

2

0

1

ns

ns

Delay time, data valid after XWE active low

4

ns

Hold time, address valid after zone chip-select inactive high

Hold time, write data valid after XWE inactive high

Data bus disabled after XR/W inactive high

ns

ns

ns

TW

2

4

Table 6

34. Synchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State)

§

MIN

MAX

UNIT

t

su(XRDYsynchL)XCOHL

t

h(XRDYsynchL)

t

e(XRDYsynchH)

t

su(XRDYsynchH)XCOHL

t

h(XRDYsynchH)XZCSH

§

The first XREADY (Synch) sample occurs with respect to E in Figure 6

30:

E =(XWRLEAD + XWRACTIVE) t

c(XTIM)

When first sampled, if XREADY (Synch) is found to be high, then the access will complete. If XREADY (Synch) is found to be low, it will be sampled

again each t

c(XTIM)

until it is found to be high.

For each sample, setup time from the beginning of the access can be calculated as:

D =(XWRLEAD + XWRACTIVE +n

1) t

c(XTIM)

t

su(XRDYsynchL)XCOHL

where n is the sample number: n = 1, 2, 3, and so forth.

Setup time, XREADY (Synch) low before XCLKOUT high/low

Hold time, XREADY (Synch) low

Earliest time XREADY (Synch) can go high before the sampling XCLKOUT edge

Setup time, XREADY (Synch) high before XCLKOUT high/low

Hold time, XREADY (Synch) held high after zone chip select high

15

12

ns

ns

ns

ns

ns

3

15

0

Table 6

35. Asynchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State)

MIN

MAX

UNIT

t

su(XRDYasynchL)XCOHL

t

h(XRDYasynchL)

t

e(XRDYasynchH)

t

su(XRDYasynchH)XCOHL

t

h(XRDYasynchH)XZCSH

The first XREADY (Synch) sample occurs with respect to E in Figure 6

31:

E = (XWRLEAD + XWRACTIVE

2) t

c(XTIM)

When first sampled, if XREADY (Asynch) is found to be high, then the access will complete. If XREADY (Asynch) is found to be low, it will be

sampled again each t

c(XTIM)

until it is found to be high.

For each sample, setup time from the beginning of the access can be calculated as:

D = (XWRLEAD + XWRACTIVE

3 + n) t

c(XTIM)

t

su(XRDYasynchL)XCOHL

where n is the sample number: n = 1, 2, 3, and so forth.

Setup time, XREADY (Asynch) low before XCLKOUT high/low

Hold time, XREADY (Asynch) low

Earliest time XREADY (Asynch) can go high before the sampling XCLKOUT edge

Setup time, XREADY (Asynch) high before XCLKOUT high/low

Hold time, XREADY (Asynch) held high after zone chip select high

11

8

ns

ns

ns

ns

ns

3

11

0

A

相关PDF资料 |

PDF描述 |

|---|---|

| TMX320R2811PBKA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMR320C2812PGFA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMR320F2811PBKA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMR320F2811PGFA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMR320F2811ZHHS | TMS320R2811, TMS320R2812 Digital Signal Processors |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMX320F28232ZHHA | 制造商:TI 制造商全称:Texas Instruments 功能描述:Digital Signal Controllers (DSCs) |

| TMX320F28232ZJZA | 制造商:TI 制造商全称:Texas Instruments 功能描述:Digital Signal Controllers (DSCs) |

| TMX320F28234ZHHA | 制造商:TI 制造商全称:Texas Instruments 功能描述:Digital Signal Controllers (DSCs) |

| TMX320F28234ZJZA | 制造商:TI 制造商全称:Texas Instruments 功能描述:Digital Signal Controllers (DSCs) |

| TMX320F28235PGFA | 功能描述:IC FLOATING POINT DSP 176-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:TMS320F28x3x Delfino™, C2000™ 产品培训模块:Asynchronous Stimulus 8-bit PIC® Microcontroller Portfolio 标准包装:42 系列:PIC® 16C 核心处理器:PIC 芯体尺寸:8-位 速度:20MHz 连通性:- 外围设备:欠压检测/复位,POR,PWM,WDT 输入/输出数:13 程序存储器容量:3.5KB(2K x 14) 程序存储器类型:OTP EEPROM 大小:- RAM 容量:128 x 8 电压 - 电源 (Vcc/Vdd):4 V ~ 5.5 V 数据转换器:A/D 4x8b 振荡器型:外部 工作温度:-40°C ~ 85°C 封装/外壳:18-SOIC(0.295",7.50mm 宽) 包装:管件 配用:XLT18SO-1-ND - SOCKET TRANSITION 18SOIC 300MILISPICR1-ND - ADAPTER IN-CIRCUIT PROGRAMMING309-1011-ND - ADAPTER 18-SOIC TO 18-DIP309-1010-ND - ADAPTER 18-SOIC TO 18-DIPAC164010-ND - MODULE SKT PROMATEII DIP/SOIC |

发布紧急采购,3分钟左右您将得到回复。