- 您现在的位置:买卖IC网 > PDF目录300044 > TSPC603PVG6LE (ATMEL CORP) 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 PDF资料下载

参数资料

| 型号: | TSPC603PVG6LE |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 |

| 封装: | 21 MM, 3.16 MM HEIGHT, 1.27 MM PITCH, CERAMIC, BGA-255 |

| 文件页数: | 22/38页 |

| 文件大小: | 599K |

| 代理商: | TSPC603PVG6LE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

TSPC603P

29/38

To ensure coherency among caches in a multiprocessor (or multiple caching-device) implementation, the 603p implemements the

MEI protocol. These three states, modified, exclusive, and invalid, indicate the state of the cache block as follows :

D Modified - The cache line is modified with respect to system memory ; that is, data for this address is valid only in the cache and

not in system memory.

D Exclusive - This cache line holds valid data that is identical to the data at this address in system memory. No other cache has

this data.

D Invalid - This cache line does not hold valid data.

Cache coherency is enforced by on-chip bus snooping logic. Since the 603p’s data cache tags are single ported, a simultaneous load

or store and snoop access represent a resource contention. The snoop access is given first access to the tags. The load or store then

occurs on the clock following snoop.

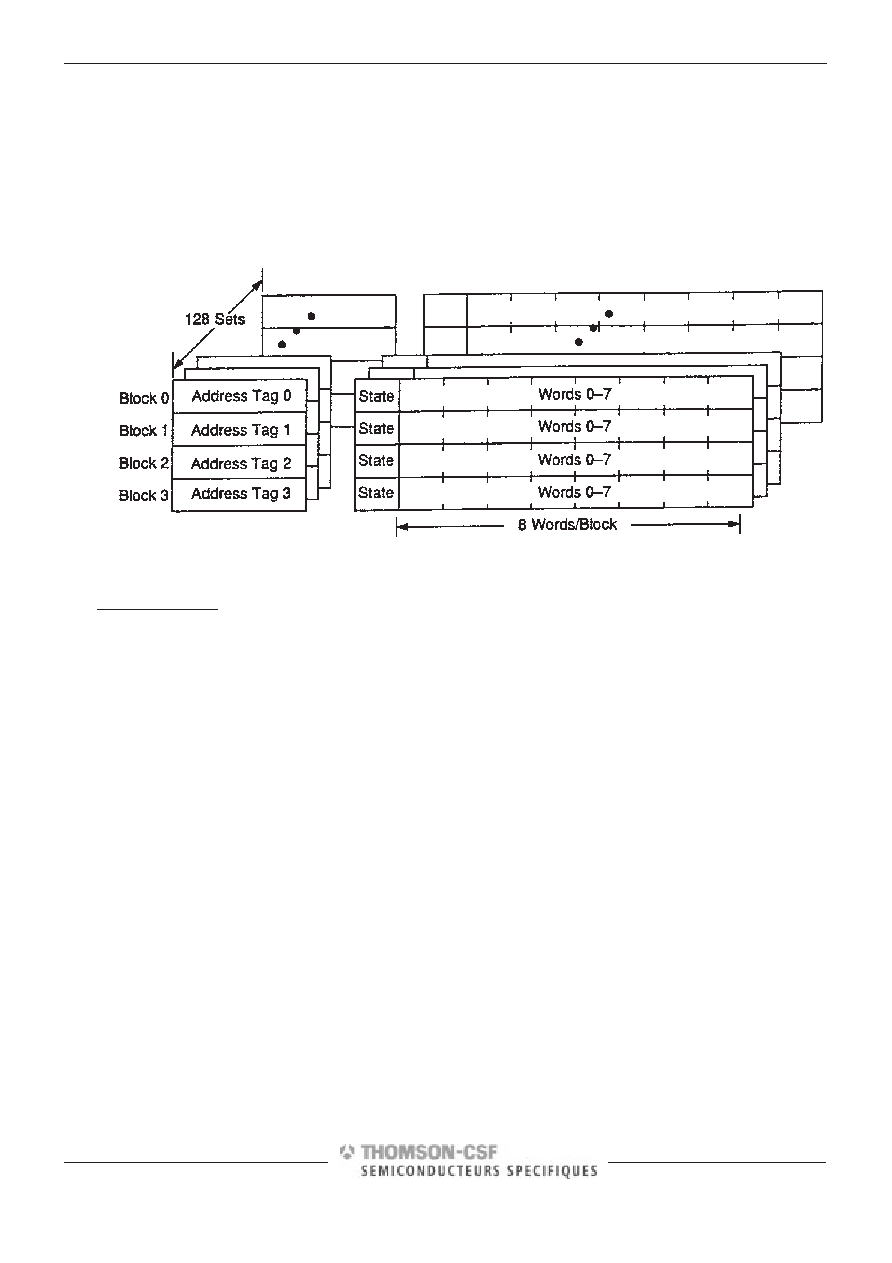

Figure 16 : Data cache organization

5.4. Exception model

The following subsections describe the PowerPC exception model and the 603p implementation, respectively.

5.4.1. PowerPC exception model

The PowerPC exception mechanism allows the processor to change to supervisor state as a result of external singles, errors, or

unusual conditions arising in the execution of instructions, and differ from the arithmetic exceptions defined by the IEEE for floating-

point operations. When exceptions occur, information about the state of the processor is saved to certain registers and the processor

begins execution at an address (exception vector) predetermined for each exception. Processing of exceptions occurs in supervisor

mode.

Although multiple exception conditions can map to a single exception vector, a more specific condition may be determined by examin-

ing a register associated with the exception - for example, the DSISR and the FPSCR. Additionally, some exception conditions can be

explicitly enable or disabled by software.

The PowerPC architecture requires that exceptions be handled in program order ; therefore, although a particular implementation

may recognize exception conditions out of order, they are presented strictly in order. When an instruction-caused exception is recog-

nized, any unexecuted instructions that appear earlier in the instruction stream, including any that have not yet entered the execute

state, are required to complete before the exception is taken. Any exceptions caused by those instructions are handled first. Likewise,

exceptions that are asynchronous and precise are recognized when they occur, but are not handled until the instruction currently in

the completion state successfully completes execution or generates an exception, and the completed store queue is emptied.

Unless a catastrophic causes a system reset or machine check exception, only one exception is handled at a time. If, for example, a

single instruction encounters multiple exception conditions, those conditions are encountered sequentially. After the exception hand-

ler handles an exception, the instruction execution continues until the next exception condition is encountered. However, in many

cases there is no attempt to re-execute the instruction. This method of recognizing and handling exception conditions sequentially

guarantees that exceptions are recoverable.

Exception handlers should save the information stored in SRR0 and SRR1 early to prevent the program state from being lost due to a

system reset and machine check exception or to an instruction-caused exception in the exception handler, and before enabling exter-

nal interrupts.

The PowerPC architecture support four types of exceptions :

相关PDF资料 |

PDF描述 |

|---|---|

| TSPDF11FGSRA0 | PUSHBUTTON SWITCH, SPDT, MOMENTARY, 0.02A, 20VDC, SURFACE MOUNT-RIGHT ANGLE |

| TSS21NGRA | SLIDE SWITCH, DPDT, LATCHED, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

| TSS901ESASL3 | 3 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, QFP196 |

| TSSH-106-01-L-D | 12 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| TSSH-108-01-T-DV | 16 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SURFACE MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSPC603R | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RCAB/Q8L | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RCAB/Q8LC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RMAB/Q8L | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RMAB/Q8LC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

发布紧急采购,3分钟左右您将得到回复。