- 您现在的位置:买卖IC网 > PDF目录199556 > UDA1345TS/N2,118 (NXP SEMICONDUCTORS) Economy audio CODEC; Package: SOT341-1 (SSOP28); Container: Reel Pack, SMD, 13" PDF资料下载

参数资料

| 型号: | UDA1345TS/N2,118 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 消费家电 |

| 英文描述: | Economy audio CODEC; Package: SOT341-1 (SSOP28); Container: Reel Pack, SMD, 13" |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封装: | 5.30 MM, PLASTIC, SSOP-28 |

| 文件页数: | 2/28页 |

| 文件大小: | 136K |

| 代理商: | UDA1345TS/N2,118 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

2002 May 28

10

Philips Semiconductors

Product specication

Economy audio CODEC

UDA1345TS

7.10

L3 microcontroller mode

The UDA1345TS is set to the L3 microcontroller mode by

setting both MC1 (pin 8) and MC2 (pin 21) LOW.

The definition of the control registers is given in

Section 7.12.

7.10.1

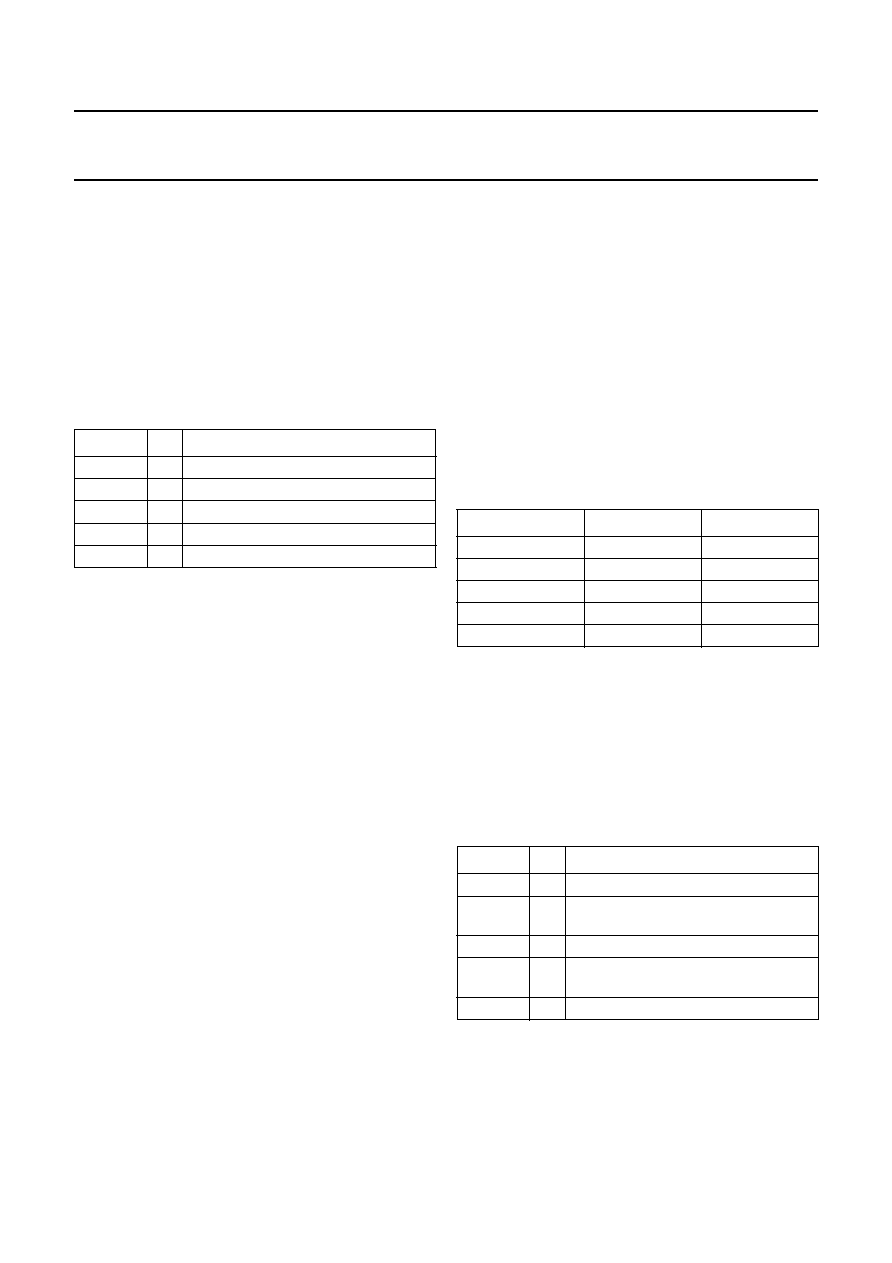

PINNING DEFINITION

The pinning definition under L3 microcontroller interface is

given in Table 5.

Table 5

Pinning denition under L3 control

7.10.2

SYSTEM CLOCK

Under L3 control the options are 256, 384 and 512fs.

7.10.3

MULTIPLE FORMAT INPUT/OUTPUT INTERFACE

The UDA1345TS supports the following data input/output

formats under L3 control:

I2S-bus with data word length of up to 24 bits

MSB-justified serial format with data word length of up to

20 bits

LSB-justified serial format with data word lengths of

16, 18 or 20 bits

Three combined data formats with MSB data output and

LSB 16, 18 and 20 bits data input.

The formats are illustrated in Fig.3. Left and right data

channel words are time multiplexed.

7.10.4

ADC INPUT VOLTAGE CONTROL

The UDA1345TS supports a 2 V (RMS) input using a

series resistor of 12 k

as described in Section 7.2. In

L3 microcontroller mode, the gain can be selected via

pin MP5.

When MP5 is set LOW, 0 dB gain is selected. When MP5

is set HIGH, 6 dB gain is selected.

7.10.5

OVERLOAD DETECTION (ADC)

In practice the output is used to indicate whenever the

output data, in either the left or right channel, is greater

than

1 dB (the actual figure is 1.16 dB) of the maximum

possible digital swing. When this condition is detected the

OVERFL output is forced HIGH for at least 512fs cycles

(11.6 ms at fs = 44.1 kHz). This time-out is reset for each

infringement.

7.10.6

DC CANCELLATION FILTER (ADC)

An optional IIR high-pass filter is provided to remove

unwanted DC components. The operation is selected by

the microcontroller via the L3-bus. The filter characteristics

are given in Table 6.

Table 6

DC cancellation lter characteristics

7.11

Static pin mode

The UDA1345TS is set to static pin control mode by setting

both MC1 (pin 8) and MC2 (pin 21) HIGH.

7.11.1

PINNING DEFINITION

The pinning definition under static pin control is given in

Table 7.

Table 7

Pinning denition for static pin control

SYMBOL PIN

DESCRIPTION

MP1

9

OVERFL output

MP2

13

L3MODE input

MP3

14

L3CLOCK input

MP4

15

L3DATA input

MP5

20

ADC 1 V or 2 V (RMS) input control

ITEM

CONDITIONS

VALUE (dB)

Pass-band ripple

none

Pass-band gain

0

Droop

at 0.00045fs

0.031

Attenuation at DC

at 0.00000036fs

>40

Dynamic range

0

0.45f

s

>110

SYMBOL PIN

DESCRIPTION

MP1

9

data input/output setting

MP2

13

3-level pin controlling de-emphasis

and mute

MP3

14

256fs or 384fs system clock

MP4

15

3-level pin to control ADC power mode

and 1 V (RMS) or 2 V (RMS) input

MP5

20

data input/output setting

相关PDF资料 |

PDF描述 |

|---|---|

| UDA1345TS/N2,112 | Economy audio CODEC; Package: SOT341-1 (SSOP28); Container: Tube |

| UDA1361TS/N1,112 | 96 kHz sampling 24-bit stereo audio ADC; Package: SOT369-1 (SSOP16); Container: Tube |

| UDA1361TS/N1,118 | 96 kHz sampling 24-bit stereo audio ADC; Package: SOT369-1 (SSOP16); Container: Reel Pack, SMD, 13" |

| UDA1380HN/N2,118 | Stereo audio coder-decoder for MD, CD and MP3; Package: SOT617-1 (HVQFN32); Container: Reel Pack, SMD, 13" |

| UDA1380TT | Stereo audio coder-decoder for MD, CD and MP3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UDA1350AH | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:IEC 958 audio DAC |

| UDA1350ATS | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:IEC 958 audio DAC |

| UDA1351 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

| UDA1351H | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

| UDA1351H/N1,551 | 功能描述:数模转换器- DAC 96 KHZ SPDIF DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。