- 您现在的位置:买卖IC网 > PDF目录199556 > UDA1345TS/N2,118 (NXP SEMICONDUCTORS) Economy audio CODEC; Package: SOT341-1 (SSOP28); Container: Reel Pack, SMD, 13" PDF资料下载

参数资料

| 型号: | UDA1345TS/N2,118 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 消费家电 |

| 英文描述: | Economy audio CODEC; Package: SOT341-1 (SSOP28); Container: Reel Pack, SMD, 13" |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封装: | 5.30 MM, PLASTIC, SSOP-28 |

| 文件页数: | 5/28页 |

| 文件大小: | 136K |

| 代理商: | UDA1345TS/N2,118 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

2002 May 28

13

Philips Semiconductors

Product specication

Economy audio CODEC

UDA1345TS

7.12

L3 interface

The UDA1345TS has a microcontroller input mode. In the

microcontroller mode, all of the digital sound processing

features and the system controlling features can be

controlled by the microcontroller. The controllable features

are:

System clock frequency

Data input format

Power control

DC filtering

De-emphasis

Volume

Mute.

The exchange of data and control information between the

microcontroller and the UDA1345TS is accomplished

through a serial hardware interface comprising the

following pins:

L3DATA: microcontroller interface data line

L3MODE: microcontroller interface mode line

L3CLOCK: microcontroller interface clock line.

Information transfer via the microcontroller bus is LSB first,

and is organized in accordance with the so called ‘L3’

format, in which two different modes of operation can be

distinguished; address mode and data transfer mode

(see Figs 4 and 5).

The address mode is required to select a device

communicating via the L3-bus and to define the

destination register set for the data transfer mode. Data

transfer for the UDA1345TS can only be in one direction:

for the UDA1345TS, data can only be written to the device.

Important: since the UDA1345TS does not have a

Power-up reset circuit, after power up the L3 interface

registers MUST be initialized.

7.12.1

ADDRESS MODE

The address mode is used to select a device for

subsequent data transfer and to define the destination

register set (DATA or STATUS). The address mode is

characterized by L3MODE being LOW and a burst of

8 pulses on L3CLOCK, accompanied by 8 data bits.

The fundamental timing is shown in Fig.4. Data

bits 0 and 1 indicate the type of subsequent data transfer

as given in Table 12.

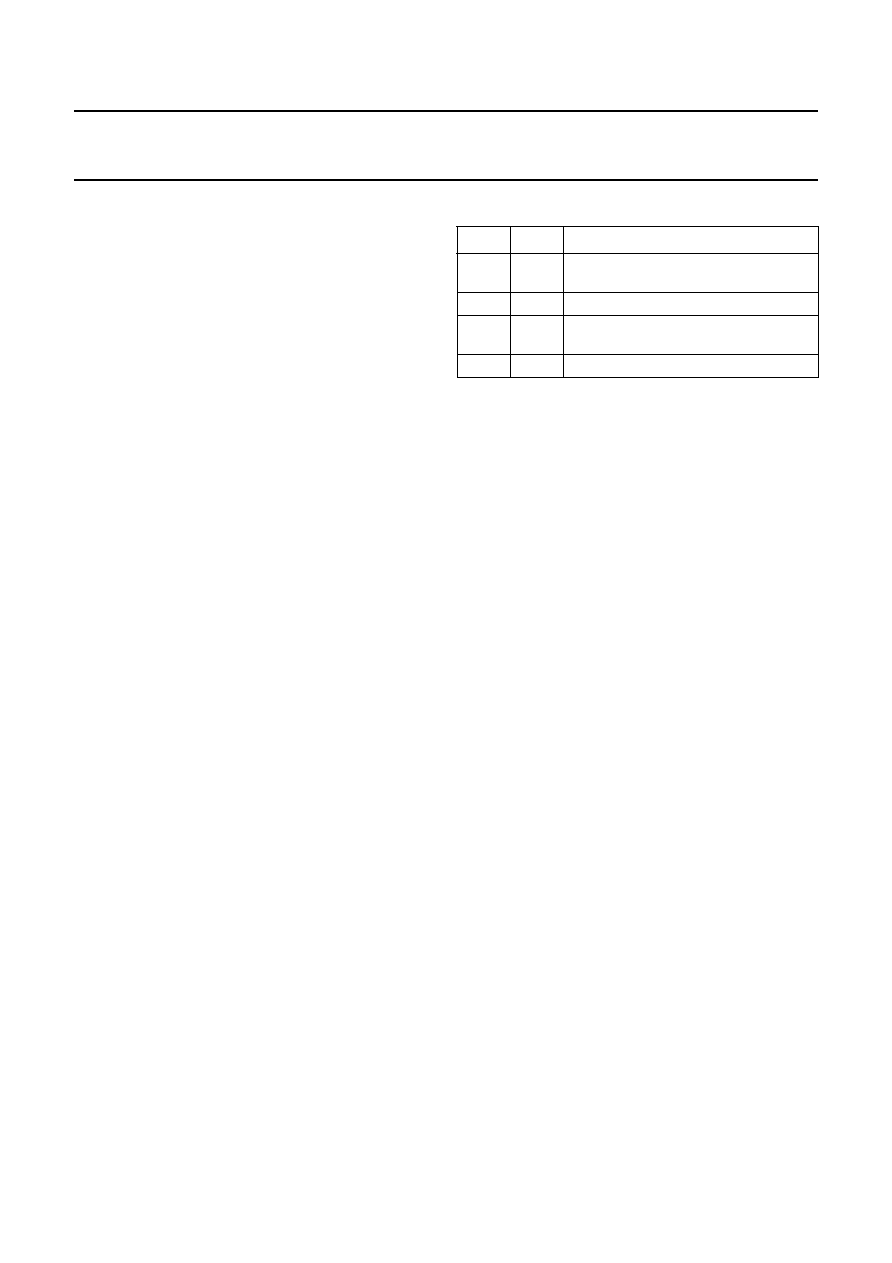

Table 12 Selection of data transfer

Data bits 7 to 2 represent a 6-bit device address, with bit 7

being the MSB and bit 2 the LSB. The address of the

UDA1345TS is 000101 (bit 7 to bit 2). In the event that the

UDA1345TS receives a different address, it will deselect

its microcontroller interface logic.

7.12.2

DATA TRANSFER MODE

The selection preformed in the address mode remains

active during subsequent data transfers, until the

UDA1345TS receives a new address command.

The fundamental timing of data transfers is essentially the

same as in the address mode, shown in Fig.4. The

maximum input clock and data rate is 128fs. All transfers

are byte wise, i.e. they are based on groups of 8 bits. Data

will be stored in the UDA1345TS after the eighth bit of a

byte has been received. A multibyte transfer is illustrated

in Fig.6.

7.12.2.1

Programming the sound processing and other

features

The feature values are stored in independent registers.

The first selection of the registers is achieved by the choice

of data type that is transferred, being DATA or STATUS.

This is performed in the address mode, bit 1 and bit 0

(see Table 12). The second selection is performed by the

2 MSBs of the data byte (bit 7 and bit 6). The other bits in

the data byte (bit 5 to bit 0) are the values that are placed

in the selected registers.

When the data transfer of type DATA is selected, the

features Volume, De-emphasis, Mute and Power control

can be controlled. When the data transfer of type STATUS

is selected, the features system clock frequency, data

input format and DC filter can be controlled.

BIT 1

BIT 0

TRANSFER

0

DATA (volume, de-emphasis, mute,

and power control)

0

1

not used

1

0

STATUS (system clock frequency, data

input format and DC lter)

1

not used

相关PDF资料 |

PDF描述 |

|---|---|

| UDA1345TS/N2,112 | Economy audio CODEC; Package: SOT341-1 (SSOP28); Container: Tube |

| UDA1361TS/N1,112 | 96 kHz sampling 24-bit stereo audio ADC; Package: SOT369-1 (SSOP16); Container: Tube |

| UDA1361TS/N1,118 | 96 kHz sampling 24-bit stereo audio ADC; Package: SOT369-1 (SSOP16); Container: Reel Pack, SMD, 13" |

| UDA1380HN/N2,118 | Stereo audio coder-decoder for MD, CD and MP3; Package: SOT617-1 (HVQFN32); Container: Reel Pack, SMD, 13" |

| UDA1380TT | Stereo audio coder-decoder for MD, CD and MP3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UDA1350AH | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:IEC 958 audio DAC |

| UDA1350ATS | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:IEC 958 audio DAC |

| UDA1351 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

| UDA1351H | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:96 kHz IEC 958 audio DAC |

| UDA1351H/N1,551 | 功能描述:数模转换器- DAC 96 KHZ SPDIF DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。