- 您现在的位置:买卖IC网 > PDF目录275205 > V54C3128164VBC7PC (PROMOS TECHNOLOGIES INC) 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 PDF资料下载

参数资料

| 型号: | V54C3128164VBC7PC |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

| 封装: | MO-210, FBGA-54 |

| 文件页数: | 6/56页 |

| 文件大小: | 734K |

| 代理商: | V54C3128164VBC7PC |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

14

V54C3128(16/80/40)4VB Rev.1.5 March 2006

ProMOS TECHNOLOGIES

V54C3128(16/80/40)4VB

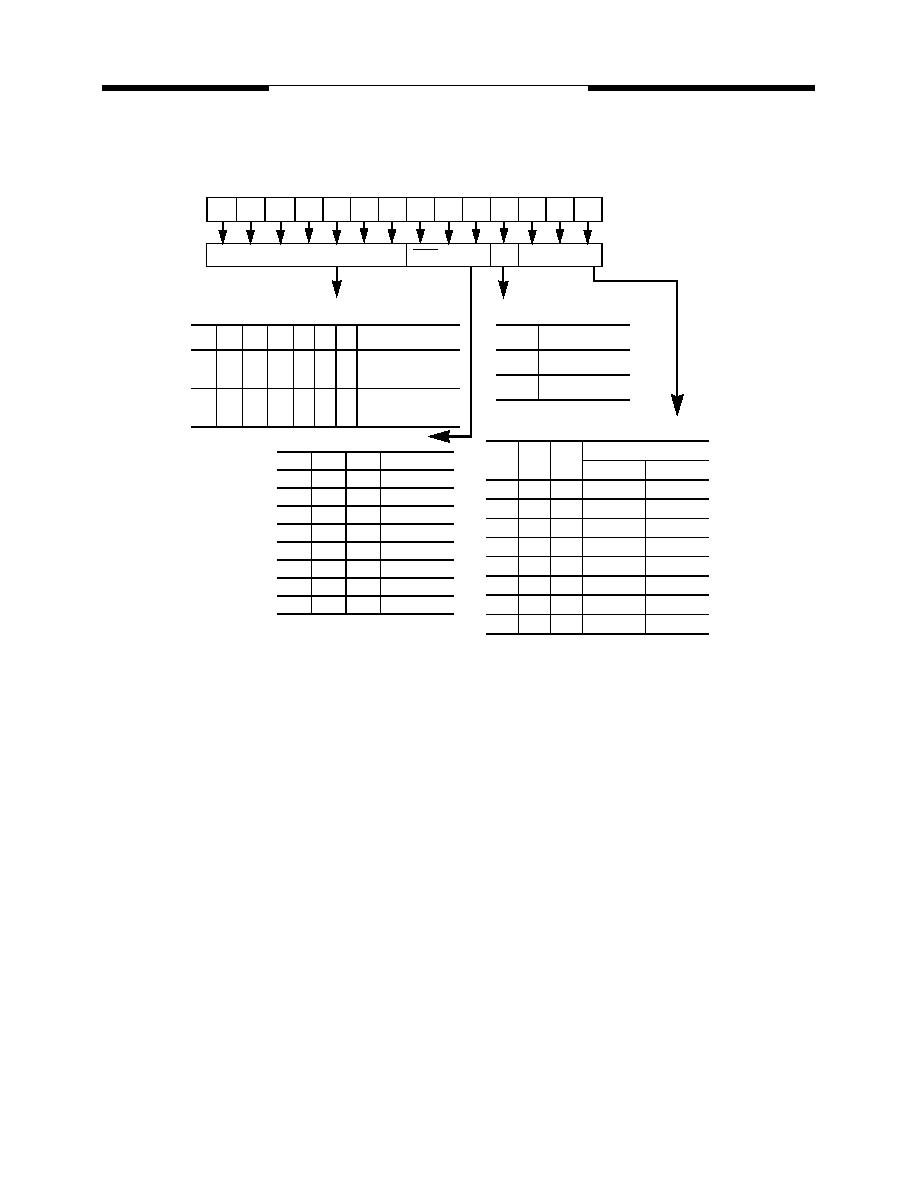

Address Input for Mode Set (Mode Register Operation)

Similar to the page mode of conventional

DRAM’s, burst read or write accesses on any col-

umn address are possible once the RAS cycle

latches the sense amplifiers. The maximum tRAS or

the refresh interval time limits the number of random

column accesses. A new burst access can be done

even before the previous burst ends. The interrupt

operation at every clock cycles is supported. When

the previous burst is interrupted, the remaining ad-

dresses are overridden by the new address with the

full burst length. An interrupt which accompanies

with an operation change from a read to a write is

possible by exploiting DQM to avoid bus contention.

When two or more

banks are activated

sequentially,

interleaved

bank

read

or

write

operations are possible. With the programmed

burst length, alternate access and precharge

operations on two or more banks can realize fast

serial data access modes among many different

pages. Once two or more banks are activated,

column to column interleave operation can be done

between different pages.

A11

A3

A4

A2

A1

A0

A10 A9

A8

A7

A6

A5

Address Bus (Ax)

BT

Burst Length

CAS Latency

Mode Register

CAS Latency

A6

A5

A4

Latency

000

Reserve

001

Reserve

010

2

011

3

100

Reserve

101

Reserve

110

Reserve

111

Reserve

Burst Length

A2

A1

A0

Length

Sequential

Interleave

00

0

1

00

1

2

01

0

4

01

1

8

1

0

Reserve

1

0

1

Reserve

1

0

Reserve

1

Full Page

Reserve

Burst Type

A3

Type

0

Sequential

1

Interleave

Operation Mode

BA1 BA0 A11 A10 A9 A8 A7

Mode

000

0

Burst Read/Burst

Write

000

0

1

0

Burst Read/Single

Write

Operation Mode

BA0

BA1

相关PDF资料 |

PDF描述 |

|---|---|

| V59C1512164QALP19 | 32M X 16 DDR DRAM, PBGA92 |

| V59C1512164QALP25E | 32M X 16 DDR DRAM, BGA92 |

| V59C1512168QALF25AE | 32M X 16 DDR DRAM, BGA92 |

| VT20C72-35JC | 4K X 4 CACHE SRAM, 35 ns, PDSO24 |

| V54C3128804VCLT6E | 16M X 8 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V54C3128164VBGA | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, BGA PACKAGE |

| V54C3128164VBI7 | 制造商:PROMOS 功能描述: 制造商:ProMOS Technologies Inc 功能描述:8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3128164VS | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C3128164VT | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C3128404VBGA | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, BGA PACKAGE |

发布紧急采购,3分钟左右您将得到回复。