- 您现在的位置:买卖IC网 > PDF目录300084 > V91F565U24QCFW-F5 (PROMOS TECHNOLOGIES INC) 128M X 72 DDR DRAM MODULE, 0.45 ns, DMA240 PDF资料下载

参数资料

| 型号: | V91F565U24QCFW-F5 |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM MODULE, 0.45 ns, DMA240 |

| 封装: | ROHS COMPLIANT, FBDIMM-240 |

| 文件页数: | 5/22页 |

| 文件大小: | 207K |

| 代理商: | V91F565U24QCFW-F5 |

V91F565U24QC Rev 1.0 May 2007

13

V91F565U24QC

ProMOS TECHNOLOGIES

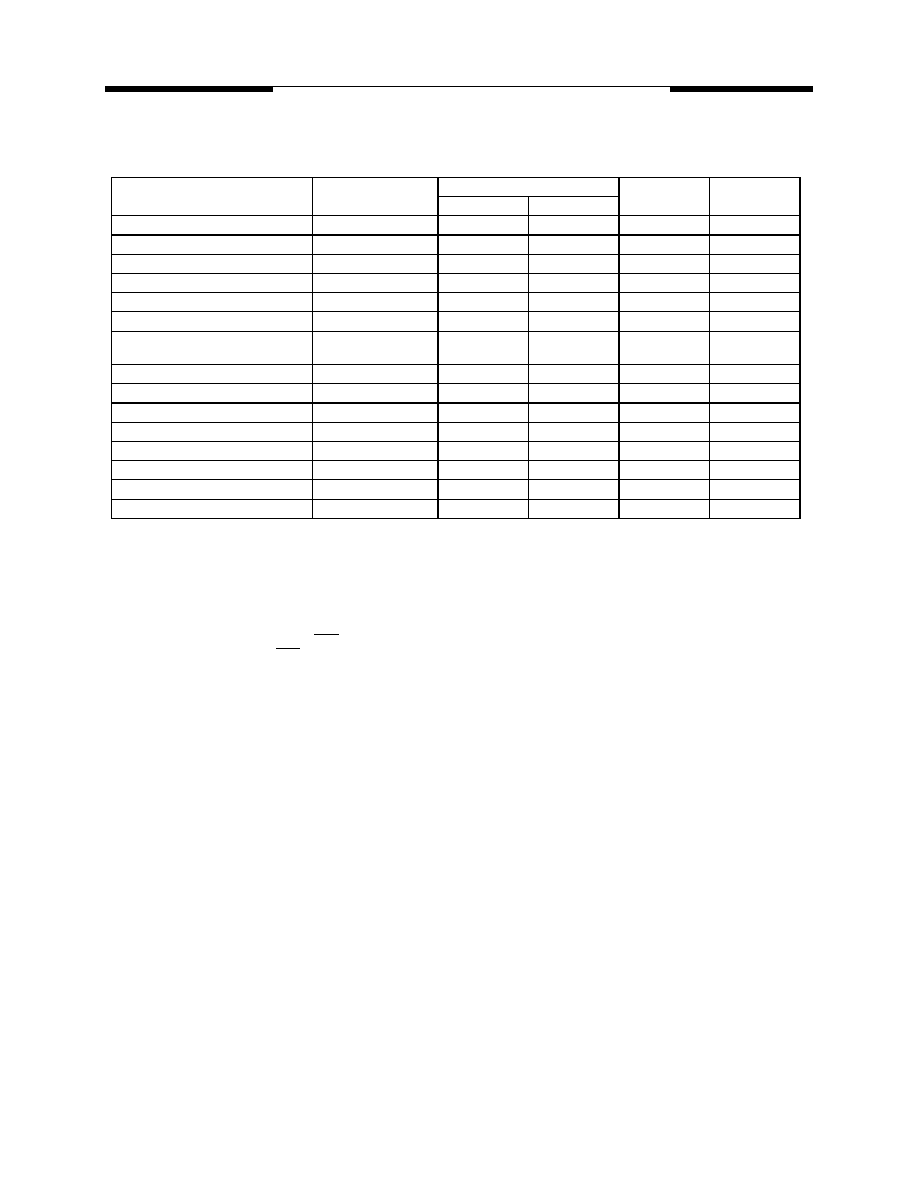

Reference Clock Input Specifications

Notes :

1.133MHz for PC2-4200 and 166MHz for PC2-5300.

2. Measured with SSC disabled.

3. Measured differentially through the range of 0.175V to 0.525V.

4. The crossing point must meet the absolute and relative crossing point specification simultaneously.

5. VCROSS_REL_(MIN) and VCROSS_REL(MAX) are derived using the following calculation : Min = 0.5(Vhavg-0.710)+0.250;and

Max=0.5(Vhavg-0.710)+0.550, where Vhavg is the average of VSCK-HIGHM.

6. Measured with a single-ended input voltage of 1V.

7. Applies to reference clocks SCK and SCK.

8. Difference between SCK and SCK input.

9. T1 = [Tdatapath-Tclockpath](excluding PLL loop delays). This parameter is not a direct clock output parameter but in indirectly deter-

mines the clock output parameter TREF-JITTER.

10. The net transport delay is the difference in time of flight between associated data and clock paths. The data path is defined from the

reference clock source, through the TX, to data arrival at the data dampling point in the RX. The clock path is defined from the reference

clock source to clock arrival at the same sampling point. The path delays are caused by copper trace routes. on-chip routing, on-chip

buffering, etc. They include the time-of flight of interpolators or other clock adjustment mechanisms. They do not include the phase

delays caused by finite PLL loop bandwidth because these delays are modeled by the PLL transfer functions.

11. Direct measurement of phase jitter records over 1016 periods is impractical. It is expected that the jitter will be measured over a small-

er, yet statistically significant, sample size and the total jitter at 1016 samples extrapolated from an estimate of the sigma of the random

jitter components.

12. Measured with SSC enabled on reference clock generator.

13. As measured after the phase jitter filter. This number is separate from the receiver jitter budget that is defined by the TRXTotal - MIN

parameters

Parameter

Symbol

Values

Units

Note

MIN

MAX

Reference clock frequency

fsck

133

200

MHz

1.2

Rise time, fall time

TSCK-RISE, TSCK-FALL

175

700

ps

3

Voltage high

VSCK-HIGH

660

850

mV

Voltage low

VSCK-LOW

-150

mV

Absolute crossing point

VCROSS-ABS

250

550

mV

4

Relative crossing

VCROSS-REL

calculated

4,5

Percent mismatch between rise and

fall times

TSCK-RISE-FALL-MATCH

-10

%

Duty cycle of reference clock

TSCK-DUTYCYCLE

40

60

%

Clock leakage current

II-CK

-10

10

uA

6,7

Clock input capacitance

CI-CK

0.5

2

pF

7

Clock input capacitance delta

CI_CK(D)

-0.25

0.25

pF

8

Transport delay

T1

5

ns

9, 10

Phase jitter sample size

NSAMPLE

1016

Periods

11

Reference clock jitter, filtered

TREF-JITTER

40

ps

12,13

Reference clock deterministic jitter

TREF-DJ

TBD

ps

相关PDF资料 |

PDF描述 |

|---|---|

| VA75-NM-NM-60 | INTERCONNECTION DEVICE |

| VA26-TP-N-60 | INTERCONNECTION DEVICE |

| VA40-TP-2.92-60 | INTERCONNECTION DEVICE |

| VB-48TBU-5 | POWER/SIGNAL RELAY, DPDT, MOMENTARY, 0.015A (COIL), 48VDC (COIL), 700mW (COIL), 5A (CONTACT), 150VDC (CONTACT), THROUGH HOLE-STRAIGHT MOUNT |

| VB-48TBU-E | POWER/SIGNAL RELAY, DPDT, MOMENTARY, 0.015A (COIL), 48VDC (COIL), 700mW (COIL), 5A (CONTACT), 150VDC (CONTACT), THROUGH HOLE-STRAIGHT MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V920 | 制造商:KNOX 制造商全称:KNOX 功能描述:ULTRA-LOW LEAKAGE ABRUPT VARACTOR DIODES |

| V920E | 制造商:TRW Inc 功能描述: |

| V9-20S13D900 | 制造商:Honeywell Sensing and Control 功能描述:Switch Snap Action N.O./N.C. SPDT Pin Plunger Quick Connect 20.1A 250VAC 745.7VA 5N Screw Mount |

| V9-20S23D900 | 功能描述:基本/快动开关 SPST-NO 20A 125VAC Round Pin Plunger RoHS:否 制造商:Omron Electronics 触点形式:SPDT 执行器:Lever 电流额定值:5 A 电压额定值 AC:250 V 电压额定值 DC:30 V 功率额定值: 工作力:120 g IP 等级:IP 67 NEMA 额定值: 端接类型:Wire 安装:Panel |

| V9-20S43D900 | 功能描述:基本/快动开关 SPDT 20A 125VAC Round Pin Plunger RoHS:否 制造商:Omron Electronics 触点形式:SPDT 执行器:Lever 电流额定值:5 A 电压额定值 AC:250 V 电压额定值 DC:30 V 功率额定值: 工作力:120 g IP 等级:IP 67 NEMA 额定值: 端接类型:Wire 安装:Panel |

发布紧急采购,3分钟左右您将得到回复。