- 您现在的位置:买卖IC网 > PDF目录245658 > W25Q16CVTCAG (WINBOND ELECTRONICS CORP) 16M X 1 SPI BUS SERIAL EEPROM, PBGA24 PDF资料下载

参数资料

| 型号: | W25Q16CVTCAG |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | PROM |

| 英文描述: | 16M X 1 SPI BUS SERIAL EEPROM, PBGA24 |

| 封装: | 8 X 6 MM, GREEN, TFBGA-24 |

| 文件页数: | 7/79页 |

| 文件大小: | 1131K |

| 代理商: | W25Q16CVTCAG |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

W25Q16CV

Publication Release Date: April 01, 2011

- 15 -

Revision C

CMP is set to 1, previous array protection set by SEC, TB, BP2, BP1 and BP0 will be reversed. For

instance, when CMP=0, a top 4KB sector can be protected while the rest of the array is not; when CMP=1,

the top 4KB sector will become unprotected while the rest of the array become read-only. Please refer to

the Status Register Memory Protection table for details. The default setting is CMP=0.

7.1.7

Status Register Protect Bits (SRP1, SRP0)

The Status Register Protect bits (SRP1 and SRP0) are non-volatile read/write bits in the status register

(S8 and S7). The SRP bits control the method of write protection: software protection, hardware

protection, power supply lock-down or one time programmable (OTP) protection.

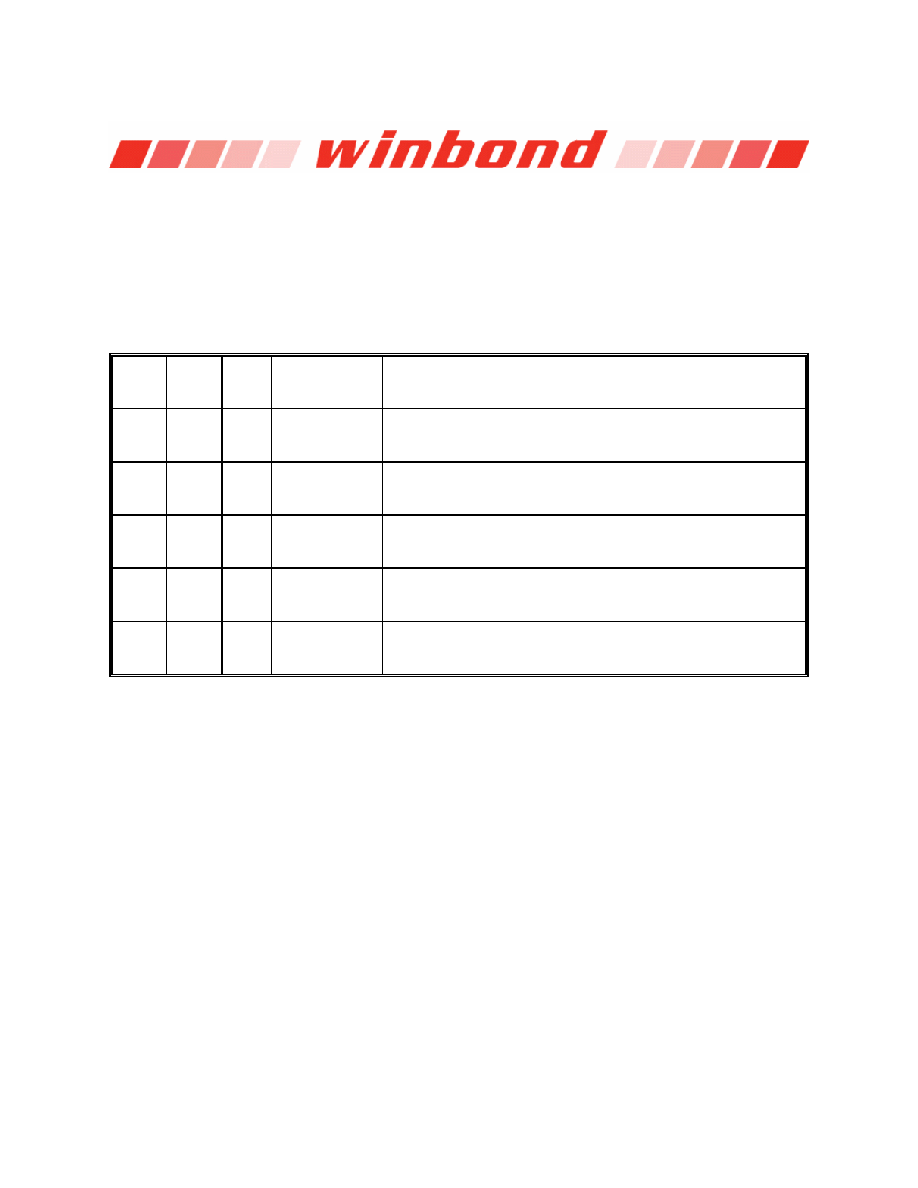

SRP1 SRP0

/WP

Status

Register

Description

0

X

Software

Protection

/WP pin has no control. The Status register can be written to

after a Write Enable instruction, WEL=1. [Factory Default]

0

1

0

Hardware

Protected

When /WP pin is low the Status Register locked and can not

be written to.

0

1

Hardware

Unprotected

When /WP pin is high the Status register is unlocked and can

be written to after a Write Enable instruction, WEL=1.

1

0

X

Power Supply

Lock-Down

Status Register is protected and can not be written to again

until the next power-down, power-up cycle.

(1)

1

X

One Time

Program

(2)

Status Register is permanently protected and can not be

written to.

Notes:

1. When SRP1, SRP0 = (1, 0), a power-down, power-up cycle will change SRP1, SRP0 to (0, 0) state. 2.

This feature is available upon special order. Please contact Winbond for details.

7.1.8

Erase/Program Suspend Status (SUS)

The Suspend Status bit is a read only bit in the status register (S15) that is set to 1 after executing a

Erase/Program Suspend (75h) instruction. The SUS status bit is cleared to 0 by Erase/Program Resume

(7Ah) instruction as well as a power-down, power-up cycle.

7.1.9

Security Register Lock Bits (LB3, LB2, LB1)

The Security Register Lock Bits (LB3, LB2, LB1) are non-volatile One Time Program (OTP) bits in Status

Register (S13, S12, S11) that provide the write protect control and status to the Security Registers. The

default state of LB[3:1] is 0, Security Registers are unlocked. LB[3:1] can be set to 1 individually using the

Write Status Register instruction. LB[3:1] are One Time Programmable (OTP), once it’s set to 1, the

corresponding 256-Byte Security Register will become read-only permanently.

7.1.10 Quad Enable Bit (QE)

The Quad Enable (QE) bit is a non-volatile read/write bit in the status register (S9) that allows Quad SPI

operation. When the QE bit is set to a 0 state (factory default), the /WP pin and /HOLD are enabled. When

相关PDF资料 |

PDF描述 |

|---|---|

| WF2M32S-100HM | 8M X 8 FLASH 5V PROM MODULE, 100 ns, CHIP66 |

| WF2M32S-100HC | 8M X 8 FLASH 5V PROM MODULE, 100 ns, CHIP66 |

| WF2M32S-120GTC | 8M X 8 FLASH 5V PROM MODULE, 120 ns, CQFP68 |

| WF2M32S-80GTM | 8M X 8 FLASH 5V PROM MODULE, 80 ns, CQFP68 |

| WPS256K16VC-20LJM | 256K X 16 STANDARD SRAM, 20 ns, PDSO44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W25Q16CVTCAP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16CVTCIG | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16CVTCIP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16CVZPAG | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16CVZPAP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

发布紧急采购,3分钟左右您将得到回复。