- 您现在的位置:买卖IC网 > PDF目录140405 > W3E32M72S-200BC (WHITE ELECTRONIC DESIGNS CORP) 32M X 72 DDR DRAM, 0.8 ns, PBGA219 PDF资料下载

参数资料

| 型号: | W3E32M72S-200BC |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 32M X 72 DDR DRAM, 0.8 ns, PBGA219 |

| 封装: | 32 X 25 MM, PLASTIC, BGA-219 |

| 文件页数: | 12/19页 |

| 文件大小: | 739K |

| 代理商: | W3E32M72S-200BC |

W3E32M72S-XBX

2

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specications without notice.

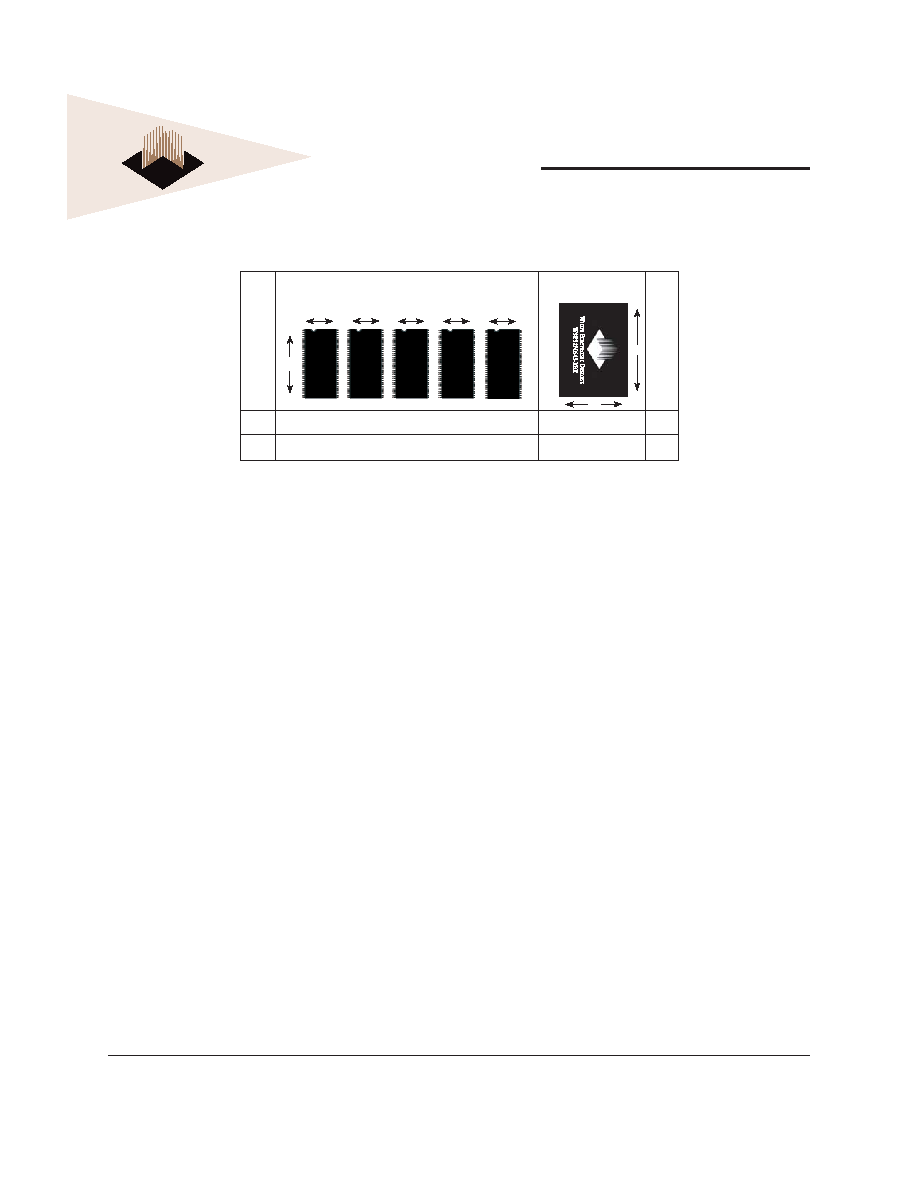

DENSITY COMPARISONS

Read and write accesses to the DDR SDRAM are burst

oriented; accesses start at a selected location and continue

for a programmed number of locations in a programmed

sequence. Accesses begin with the registration of an

ACTIVE command, which is then followed by a READ or

WRITE command. The address bits registered coincident

with the ACTIVE command are used to select the bank

and row to be accessed. The address bits registered

coincident with the READ or WRITE command are used

to select the bank and the starting column location for the

burst access.

The DDR SDRAM provides for programmable READ

or WRITE burst lengths of 2, 4, or 8 locations. An auto

precharge function may be enabled to provide a self-

timed row precharge that is initiated at the end of the

burst access.

The pipelined, multibank architecture of DDR SDRAMs allows

for concurrent operation, thereby providing high effective

bandwidth by hiding row precharge and activation time.

An auto refresh mode is provided, along with a power-

saving power-down mode. All inputs are compatible with

the Jedec Standard for SSTL_2. All full drive options

outputs are SSTL_2, Class II compatible.

Area

5 x 265mm2 = 1325mm2

800mm2

40%

5 x 66 pins = 330 pins

219 Balls

34%

S

A

V

I

N

G

S

I/O

Count

TSOP Approach (mm)

22.3

11.9

66

TSOP

11.9

66

TSOP

11.9

66

TSOP

11.9

66

TSOP

11.9

66

TSOP

Actual Size

W3E32M72S-XBX

22

16

FUNCTIONAL DESCRIPTION

Read and write accesses to the DDR SDRAM are burst

oriented; accesses start at a selected location and continue

for a programmed number of locations in a programmed

sequence. Accesses begin with the registration of an

ACTIVE command which is then followed by a READ or

WRITE command. The address bits registered coincident

with the ACTIVE command are used to select the bank and

row to be accessed (BA0 and BA1 select the bank, A0-12

select the row). The address bits registered coincident

with the READ or WRITE command are used to select the

starting column location for the burst access.

Prior to normal operation, the DDR SDRAM must be

initialized. The following sections provide detailed

information covering device initialization, register denition,

command descriptions and device operation.

INITIALIZATION

DDR SDRAMs must be powered up and initialized in a

predened manner. Operational procedures other than

those specied may result in undened operation. Power

must rst be applied to VCC and VCCQ simultaneously, and

then to VREF (and to the system VTT). VTT must be applied

相关PDF资料 |

PDF描述 |

|---|---|

| W3E32M72S-266BM | 32M X 72 DDR DRAM, 0.75 ns, PBGA219 |

| W72M64VB70BM | SPECIALTY MEMORY CIRCUIT, PBGA159 |

| WF128K32N-120G2UI5 | FLASH 5V PROM MODULE, CQFP68 |

| WF128K32N-50G2UC5 | FLASH 5V PROM MODULE, CQFP68 |

| WMS128K8L-120DRQ | 128K X 8 STANDARD SRAM, 120 ns, CDSO32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3E32M72S-200BI | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 200 MHZ, 219 PBGA, INDUSTRIAL TEMP. - Bulk |

| W3E32M72S-200BM | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 200 MHZ, 219 PBGA, MIL-TEMP. - Bulk |

| W3E32M72S-200SBC | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 200 MHZ, 208 PBGA, COMMERCIAL TEMP. - Bulk |

| W3E32M72S-200SBI | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 200 MHZ, 208 PBGA, INDUSTRIAL TEMP. - Bulk |

| W3E32M72S-200SBM | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 200 MHZ, 208 PBGA, MIL-TEMP. - Bulk |

发布紧急采购,3分钟左右您将得到回复。