- 您现在的位置:买卖IC网 > PDF目录276857 > W3H128M64E2-400SBC (MICROSEMI CORP-PMG MICROELECTRONICS) DDR DRAM, PBGA208 PDF资料下载

参数资料

| 型号: | W3H128M64E2-400SBC |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM, PBGA208 |

| 封装: | 16 X 22 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件页数: | 19/31页 |

| 文件大小: | 989K |

| 代理商: | W3H128M64E2-400SBC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

W3H128M64E-XSBX

26

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

October 2008

Rev. 1

ADVANCED

White Electronic Designs Corp. reserves the right to change products or specications without notice.

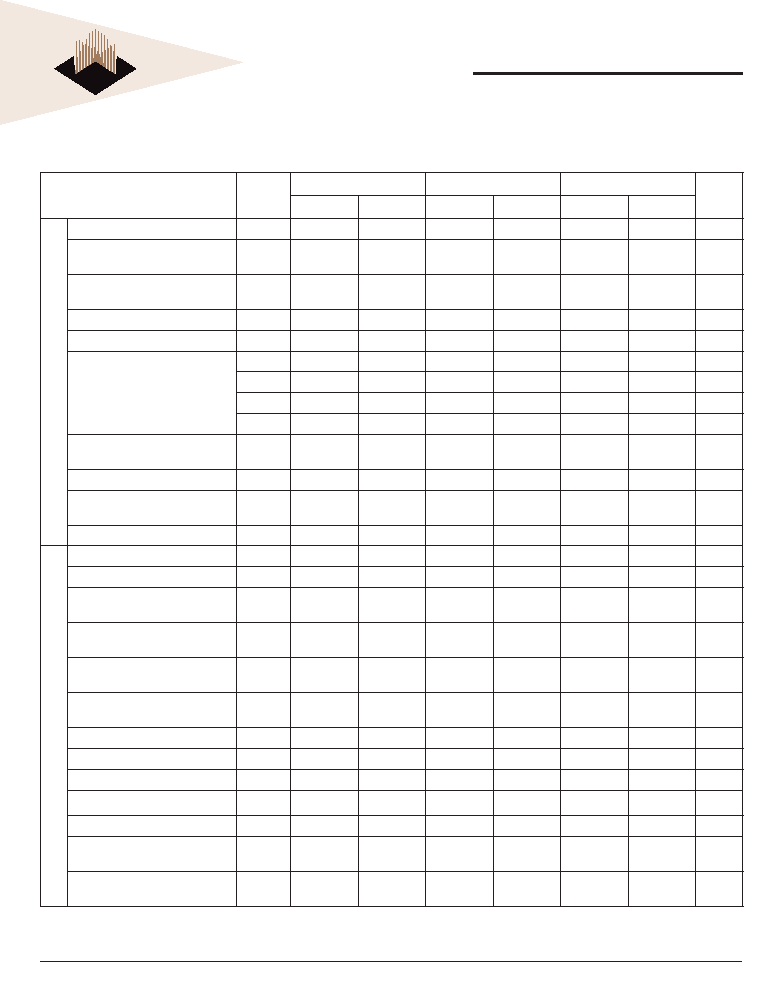

AC TIMING PARAMETERS

(continued)

-55°C ≤ TA < +125°C

Parameter

Symbol

667Mbs CL6

533Mbs CL5

400Mbs CL4

Unit

Min

Max

Min

Max

Min

Max

Data

DQ hold skew factor

t

QHS

-

340

-

400

-

450

ps

DQ output access time from CK/

CK#

t

AC

-450

450

-500

+500

-600

+600

ps

Data-out high impedance window

from CK/CK#

t

HZ

tAC(MAX)

ps

DQS Low-Z window from CK/CK#

t

LZ1

tAC(MN)

tAC(MAX)

tAC(MN)

tAC(MAX)

tAC(MN)

tAC(MAX)

ps

DQ Low-Z window from CK/CK#

t

LZ2

2*tAC(MN)

tAC(MAX)

2*tAC(MN)

tAC(MAX)

2*tAC(MN)

tAC(MAX)

ps

DQ and DM input setup time

relative to DQS

t

DSa

300

350

400

ps

t

DHa

300

350

400

ps

t

DSb

100

150

ps

t

DHb

175

225

275

ps

DQ and DM input pulse width (for

each input)

t

DIPW

0.35

ps

Data hold skew factor

t

QHS

340

400

450

ps

DQ-DQS hold, DQS to rst DQ to

go nonvalid, per access

t

QH

tHP - tQHS

ps

Data valid output window (DVW)

t

DVW

tQH - tDQSQ

ns

Data

Strobe

DQS input high pulse width

t

DQSH

0.35*tCK

tCK

DQS input low pulse width

t

DQSL

0.35*tCK

tCK

DQS output access time fromCK/

CK#

t

DQSCK

-400

400

-450

+450

-500

+500

ps

DQS falling edge to CK rising -

setup time

t

DSS

0.2*tCK

tCK

DQS falling edge from CK rising -

hold time

t

DSH

0.2*tCK

tCK

DQS-DQ skew, DOS to last DQ

valid, per group, per access

t

DQSQ

240

300

350

ps

DQS read preamble

t

RPRE

0.9*tCK

1.1*tCK

0.9*tCK

1.1*tCK

0.9*tCK

1.1*tCK

tCK

DQS read postamble

t

RPST

0.4*tCK

0.6*tCK

0.4*tCK

0.6*tCK

0.4*tCK

0.6*tCK

tCK

DQS write preamble setup time

t

WPRES

0

ps

DQS write preamble

t

WPRE

0.35

0.25

tCK

DQS write postamble

t

WPST

0.4*tCK

0.6*tCK

0.4*tCK

0.6*tCK

0.4*tCK

0.6*tCK

tCK

Positive DQS latching edge to

associated clock edge

t

DQSS

-0.25*tCK

0.25*tCK

-0.25*tCK

0.25*tCK

-0.25*tCK

0.25*tCK

tCK

Write command to rst DQS

latching transition

WL-TDQSS

WL+TDQSS

WL-TDQSS

WL+TDQSS

WL-TDQSS

WL+TDQSS

tCK

相关PDF资料 |

PDF描述 |

|---|---|

| W3HG264M72EER806AD7MG | 128M X 72 DDR DRAM MODULE, DMA244 |

| W7NCF01GH21ISBCG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF256H30IS7DG | 16M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| WED3DG7266V7D1-MG | 64M X 72 SYNCHRONOUS DRAM MODULE, ZMA144 |

| WED7G385ATA33XDI25 | 192M X 16 FLASH 3.3V PROM MODULE, DMA144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3H128M64E-400SBI | 制造商:Microsemi Corporation 功能描述:128M X 64 DDR2, 1.8V, 400MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H128M72E-400SBC | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H128M72E-400SBI | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA INDUSTRIAL TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H128M72E-400SBM | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA MIL-TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H128M72E-533NBI | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 533MHZ, 208PBGA IND TEMP. - Bulk |

发布紧急采购,3分钟左右您将得到回复。