- 您现在的位置:买卖IC网 > PDF目录276857 > W3H128M64E2-400SBC (MICROSEMI CORP-PMG MICROELECTRONICS) DDR DRAM, PBGA208 PDF资料下载

参数资料

| 型号: | W3H128M64E2-400SBC |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM, PBGA208 |

| 封装: | 16 X 22 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件页数: | 31/31页 |

| 文件大小: | 989K |

| 代理商: | W3H128M64E2-400SBC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页

W3H128M64E-XSBX

9

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

October 2008

Rev. 1

ADVANCED

White Electronic Designs Corp. reserves the right to change products or specications without notice.

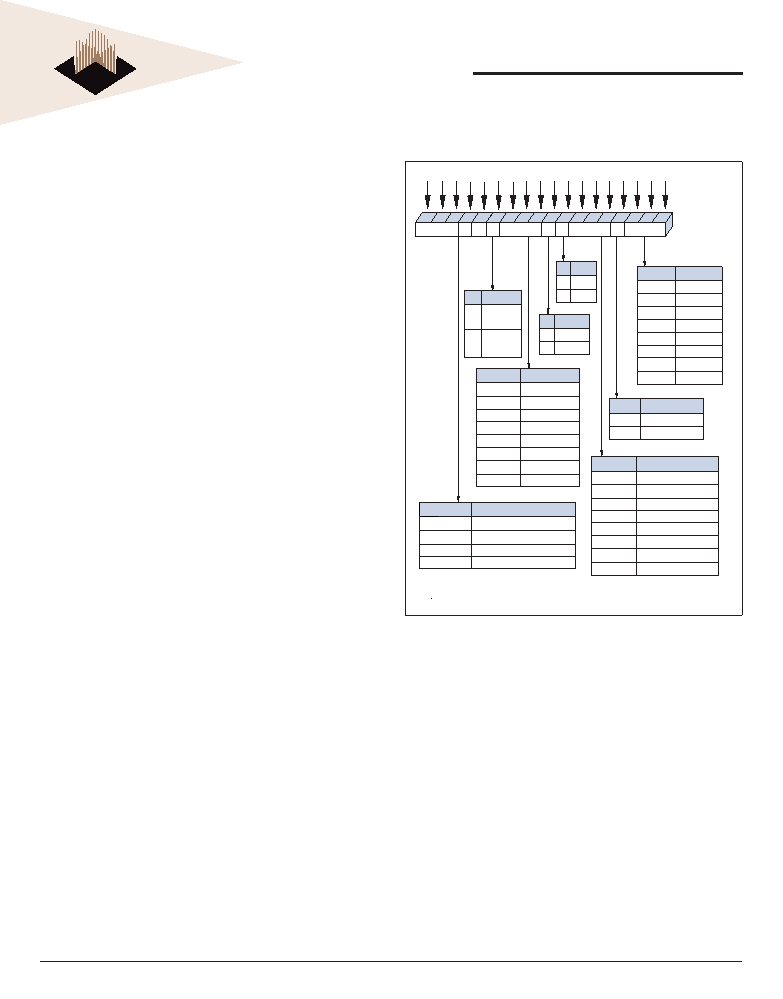

MODE REGISTER (MR)

The mode register is used to dene the specic mode of

operation of the DDR2 SDRAM. This denition includes

the selection of a burst length, burst type, CL, operating

mode, DLL RESET, write recovery, and power-down mode,

as shown in Figure 5. Contents of the mode register can be

altered by re-executing the LOAD MODE (LM) command.

If the user chooses to modify only a subset of the MR

variables, all variables (M0–M14) must be programmed

when the command is issued.

The mode register is programmed via the LM command

(bits BA2–BA0 = 0, 0, 0) and other bits (M12–M0) will

retain the stored information until it is programmed again

or the device loses power (except for bit M8, which is

self-clearing). Reprogramming the mode register will

not alter the contents of the memory array, provided it is

performed correctly.

The LM command can only be issued (or reissued) when all

banks are in the precharged state (idle state) and no bursts

are in progress. The controller must wait the specied

time tMRD before initiating any subsequent operations

such as an ACTIVE command. Violating either of these

requirements will result in unspecied operation.

BURST LENGTH

Burst length is dened by bits M0–M3, as shown in Figure

5. Read and write accesses to the DDR2 SDRAM are

burst-oriented, with the burst length being programmable

to either four or eight. The burst length dete rmines

the maximum number of column locations that can be

accessed for a given READ or WRITE command.

When a READ or WRITE command is issued, a block of

columns equal to the burst length is effectively selected.

All accesses for that burst take place within this block,

meaning that the burst will wrap within the block if a

boundary is reached. The block is uniquely selected by

A2–Ai when BL = 4 and by A3–Ai when BL = 8 (where

Ai is the most signicant column address bit for a given

conguration). The remaining (least signicant) address

bit(s) is (are) used to select the starting location within the

block. The programmed burst length applies to both READ

and WRITE bursts.

BURST TYPE

Accesses within a given burst may be programmed to be

either sequential or interleaved. The burst type is selected

via bit M3, as shown in Figure 5. The ordering of accesses

within a burst is determined by the burst length, the burst

type, and the starting column address, as shown in Table

2. DDR2 SDRAM supports 4-bit burst mode and 8-bit burst

mode only. For 8-bit burst mode, full interleave address

ordering is supported; however, sequential address

ordering is nibble-based.

Burst Length

CAS# Latency BT

PD

A9

A7 A6 A5 A4 A3

A8

A2 A1 A0

Mode Register (Mx)

Address Bus

97

6

5

4

3

82

1

0

A10

A12 A11

BA0

BA1

BA2

10

11

12

13

0

14

Burst Length

Reserved

4

8

Reserved

M0

0

1

0

1

0

1

0

1

M1

0

1

0

1

M2

0

1

0

1

Burst Type

Sequential

Interleaved

M3

CAS Latency (CL)

Reserved

3

4

5

6

Reserved

M4

0

1

0

1

0

1

0

1

M5

0

1

0

1

M6

0

1

0

1

Mo de

Normal

Test

M7

15

16

17

DLL TM

0

1

DLL Reset

No

Yes

M8

WRITE RECOVERY

Reserved

2

3

4

5

6

Reserved

M9

0

1

0

1

0

1

0

1

M10

0

1

0

1

M11

0

1

WR

A13

A14

MR

0

1

0

1

Mo de Register Definition

Mode Register (MR)

Extended Mode Register (EMR)

Extended Mode Register (EMR2)

Extended Mode Register (EMR3)

M16

0

1

M17

0

1

PD mode

Fast Exit

(Normal)

Slow Exit

(Low Power)

M12

M15

FIGURE 5 – MODE REGISTER (MR) DEFINITION

Note: Not all listed CL options are supported in any individual speed grades.

A14 is not used on this device

相关PDF资料 |

PDF描述 |

|---|---|

| W3HG264M72EER806AD7MG | 128M X 72 DDR DRAM MODULE, DMA244 |

| W7NCF01GH21ISBCG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF256H30IS7DG | 16M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| WED3DG7266V7D1-MG | 64M X 72 SYNCHRONOUS DRAM MODULE, ZMA144 |

| WED7G385ATA33XDI25 | 192M X 16 FLASH 3.3V PROM MODULE, DMA144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3H128M64E-400SBI | 制造商:Microsemi Corporation 功能描述:128M X 64 DDR2, 1.8V, 400MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H128M72E-400SBC | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H128M72E-400SBI | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA INDUSTRIAL TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H128M72E-400SBM | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA MIL-TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H128M72E-533NBI | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 533MHZ, 208PBGA IND TEMP. - Bulk |

发布紧急采购,3分钟左右您将得到回复。