- 您现在的位置:买卖IC网 > PDF目录231502 > W3HG128M72AEF665F1MCG (WHITE ELECTRONIC DESIGNS CORP) DDR DRAM MODULE, DMA240 PDF资料下载

参数资料

| 型号: | W3HG128M72AEF665F1MCG |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM MODULE, DMA240 |

| 封装: | ROHS COMPLIANT, FBDIMM-240 |

| 文件页数: | 14/17页 |

| 文件大小: | 256K |

| 代理商: | W3HG128M72AEF665F1MCG |

W3HG128M72AEF-Fx

September 2007

Rev. 3

ADVANCED*

6

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

AMB INTERFACE

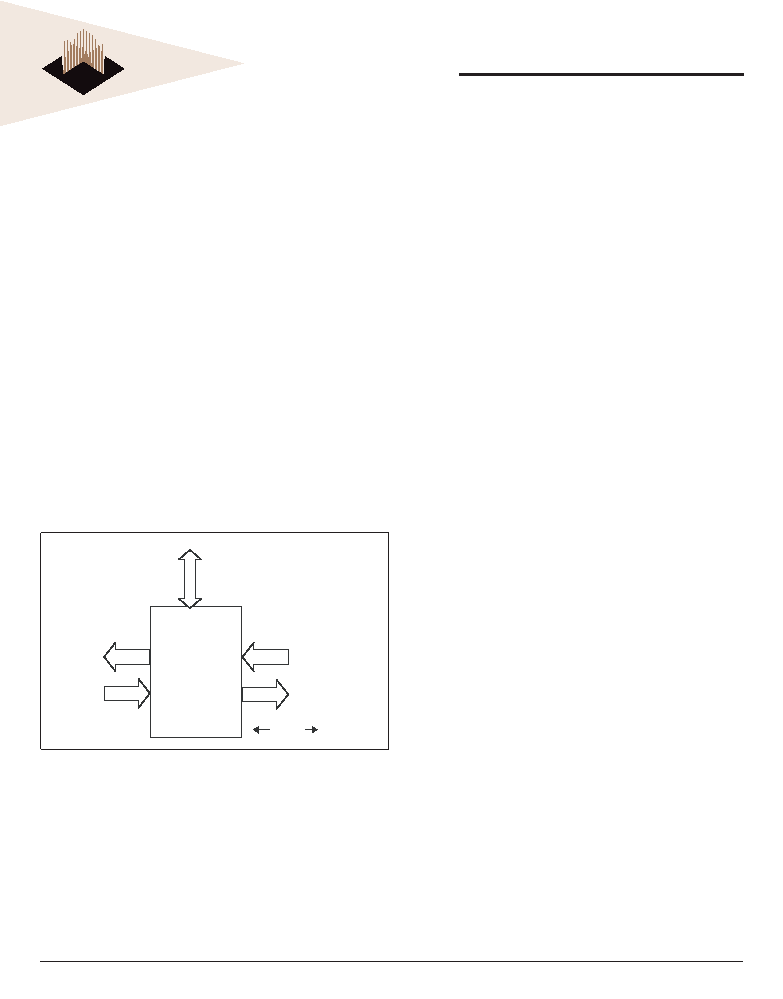

Figure 2: The AMB Interface Block Diagram illustrates

the AMB and all of its interfaces. They consist of two

FBDIMM links, one DDR2 channel and an SMBus

interface. Each FBDIMM link connects the AMB to a

host memory controller or an adjacent FBDIMM. The

DDR2 channel supports direct connection to the DDR2

SDRAM on an FBDIMM.

The FBDIMM channel uses a daisy-chain topology to

proved expansion from a single FBDIMM per channel

to up to eight FBDIMMs per channel. The host sends

data on the southbound link to the first FBDIMM, where

it is received and redriven to the second FBDIMM. On

the southbound data path, each FBDIMM receives the

data and redrives the data to the next FBDIMM, until the

last FBDIMM receives the data. The last FBDIMM in the

chain initiates the transmission of northbound data in

the direction of the host. On the northbound data path,

each FBDIMM receives the data and redrives the data

to the next FBDIMM until the host is reached.

HIGH-SPEED, DIFFERENTIAL, POINT-

TO-POINT LINK (AT 1.5V) INTERFACES

The AMB supports one FBDIMM channel consisting

of two bidirectional link interfaces using high-speed

differential point-to-point electrical signaling. The

southbound input link is 10 lanes wide. It carries

commands and write data from the host memory

controller, or the adjacent FBDIMM in the host direction,

to the next FBDIMM in the chain.

The northbound input link is 14 lanes wide. It carries

read return data or status information from one FBDIMM

to the next in the host direction and multiplexes in

any internally generated READ return data or status

information.

Data and commands sent to the DDR2 SDRAM devices

travel southbound on 10 primary differential signal

line pairs. Data and status information received from

the DDR2 SDRAM devices travel northbound on 14

primary differential pairs. Data and commands sent to

the adjacent FBDIMM are repeated and travel further

southbound on 10 secondary differential pairs. Data

and status information received from the upstream

adjacent FBDIMM travel further northbound on 14

secondary differential parts.

DDR2 CHANNEL

The AMB DDR2 channel on the advanced memory

buffer supports direct connection to DDR2 SDRAM

devices. The DDR2 channel supports two ranks of eight

banks with 16 row/column-request, 64 data, and eight

check-bit signals. There are two copies of address

and command signals to support FBDIMM routing and

electrical requirements. Four transfer burst are driven

on the data and check-bit lines at 800 MHz.

Propagation delays can differ between read data/check-

bit strobe lanes on a given channel. Each strobe

can be calibrated by hardware state machines using

WRITE/READ trial and error. Hardware aligns the

read data and check-bits to a single core clock. The

AMB provides four copies of the command clock phase

reference (CLK[3:0]) and write data/check-bit strobes

(DQS) for each DDR2 SDRAM device nibble.

SMBus SLAVE INTERFACE

The AMB supports a SMBus interface allows system

access to configuration registers independent of the

FBDIMM link. The AMB will never be a master on

the SMBus, only a slave. Serial SMBus data transfer

is supported at 100KHz. SMBus access to the AMB

may be a requirement to boot and to set link strength,

frequency and other parameters needed to ensure

robust configurations. It is also required for diagnostic

AMB

MEMORYINTERFACE

SMBus

2

R

D

L

E

N

A

H

C

r

o

y

r

a

m

i

r

P

n

o

i

t

c

e

r

i

D

t

s

o

H

NBFBD

InLink

NBFBD

Out Link

SBFBD

Out Link

SBFBD

In Link

Secondary direction or to

(optional) next FBDIMM

FIGURE 2: AMB Interface Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| WS128K32-100G4QE | 512K X 8 MULTI DEVICE SRAM MODULE, 100 ns, CQFP68 |

| WS128K32N-70HME | 512K X 8 MULTI DEVICE SRAM MODULE, 70 ns, CHIP66 |

| WPS512K32-15PJI | 2M X 8 MULTI DEVICE SRAM MODULE, 15 ns, PQMA68 |

| WMD4M4V-80F2M | 4M X 4 FAST PAGE DRAM, 80 ns, CDSO24 |

| WMS128K8L-20FEMA | 128K X 8 STANDARD SRAM, 20 ns, CDFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3HG2128M72ACER403AD6XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP |

| W3HG2128M72ACER534AD6XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP |

| W3HG2128M72ACER665AD6XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP |

| W3HG2128M72ACER806AD6XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP |

| W3HG2128M72ACER-AD6 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP |

发布紧急采购,3分钟左右您将得到回复。