- 您现在的位置:买卖IC网 > PDF目录231502 > WED2ZL361MS26BC (WHITE ELECTRONIC DESIGNS CORP) 1M X 36 ZBT SRAM, 2.6 ns, PBGA119 PDF资料下载

参数资料

| 型号: | WED2ZL361MS26BC |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | SRAM |

| 英文描述: | 1M X 36 ZBT SRAM, 2.6 ns, PBGA119 |

| 封装: | PLASTIC, BGA-119 |

| 文件页数: | 1/12页 |

| 文件大小: | 645K |

| 代理商: | WED2ZL361MS26BC |

1

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

WED2ZL361MS

Oct, 2002

Rev. 5

White Electronic Designs Corp. reserves the right to change products or specications without notice.

The WEDC SyncBurst - SRAM family employs high-speed,

low-power CMOS designs that are fabricated using an

advanced CMOS process. WEDC’s 32Mb SyncBurst

SRAMs integrate two 1M x 18 SRAMs into a single BGA

package to provide 1M x 36 conguration. All synchronous

inputs pass through registers controlled by a positive-

edge-triggered single-clock input (CK). The NBL or No

Bus Latency Memory utilizes all the bandwidth in any

combination of operating cycles. Address, data inputs, and

all control signals except output enable and linear burst

order are synchronized to input clock. Burst order control

must be tied “High or Low.” Asynchronous inputs include the

sleep mode enable (ZZ). Output Enable controls the outputs

at any given time. Write cycles are internally self-timed and

initiated by the rising edge of the clock input. This feature

eliminates complex off-chip write pulse generation and

provides increased timing exibility for incoming signals.

1Mx36 Synchronous Pipeline Burst NBL SRAM

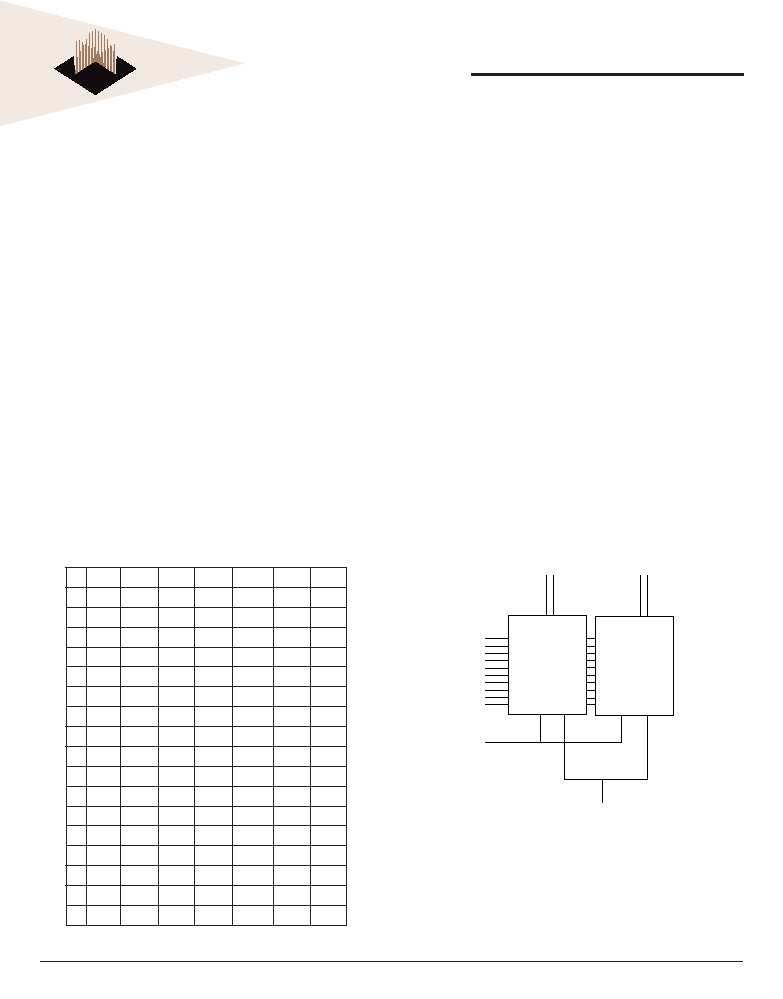

BLOCK DIAGRAM

PIN CONFIGURATION

(TOP VIEW)

Address Bus

(SA0 - SA19)

DQa, DQb

DQPa, DQPb

DQc, DQd

DQPc, DQPd

DQa - DQd

DQPa - DQPd

1M x 18

CK

CKE#

ADV#

LBO#

CS1#

CS2

CS2#

OE#

WE#

ZZ

CK

CKE#

ADV#

LBO#

CE1#

CE2

CE2#

OE#

WE#

ZZ

CK

CKE#

ADV#

LBO#

CS1#

CS2

CS2#

OE#

WE#

ZZ

BWd#

BW

a#

BWc#

BWb#

Fast clock speed: 250, 225, 200, 166, 150,

133MHz

Fast access times: 2.6, 2.8, 3.0, 3.5, 3.8, 4.2ns

Fast OE# access times: 2.6, 2.8, 3.0, 3.5, 3.8,

4.2ns

Separate +2.5V ± 5% power supplies for Core, I/O

(VCC, VCCQ)

Snooze Mode for reduced-standby power

Individual Byte Write control

Clock-controlled and registered addresses, data

I/Os and control signals

Burst control (interleaved or linear burst)

Packaging:

119-bump BGA package

Low capacitive bus loading

1

2

3

4

5

6

7

A VCCQ

SA

VCCQ

B

SA

CE2

SA

ADV#

SA

CE2#

NC

C NC

SA

VCC

SA

NC

D DQc DQPc VSS

NC

VSS

DQPb DQb

E DQc DQc

VSS

CE1#

VSS

DQb DQb

F VCCQ DQc

VSS

OE#

VSS

DQb VCCQ

G DQc DQc BWc#

SA

BWb# DQb DQb

H DQc DQc

VSS

WE#

VSS

DQb DQb

J VCCQ VCC

NC

VCC

NC

VCC

VCCQ

K DQd DQd

VSS

CK

VSS

DQa DQa

L DQd DQd BWd# NC

BWa# DQa DQa

M VCCQ DQd

VSS CKE#

VSS

DQa VCCQ

N DQd DQd

VSS

SA1

VSS

DQa DQa

P DQd DQPd VSS

SA0

VSS

DQPa DQa

R NC

SA

LBO# VCC

NC

SA

NC

T NC

NC

SA

NC

ZZ

U VCCQ

NC

VCCQ

FEATURES

DESCRIPTION

NOTE: NBL (No Bus Latency) is equivalent to ZBT

相关PDF资料 |

PDF描述 |

|---|---|

| W3E32M72S-266BC | 32M X 72 DDR DRAM, 0.75 ns, PBGA219 |

| W3HG128M72AEF665F1MCG | DDR DRAM MODULE, DMA240 |

| WS128K32-100G4QE | 512K X 8 MULTI DEVICE SRAM MODULE, 100 ns, CQFP68 |

| WS128K32N-70HME | 512K X 8 MULTI DEVICE SRAM MODULE, 70 ns, CHIP66 |

| WPS512K32-15PJI | 2M X 8 MULTI DEVICE SRAM MODULE, 15 ns, PQMA68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WED2ZL361MS26BI | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1Mx36 Synchronous Pipeline Burst NBL SRAM |

| WED2ZL361MS28BC | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1Mx36 Synchronous Pipeline Burst NBL SRAM |

| WED2ZL361MS28BI | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1Mx36 Synchronous Pipeline Burst NBL SRAM |

| WED2ZL361MS30BC | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1Mx36 Synchronous Pipeline Burst NBL SRAM |

| WED2ZL361MS30BI | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1Mx36 Synchronous Pipeline Burst NBL SRAM |

发布紧急采购,3分钟左右您将得到回复。