- 您现在的位置:买卖IC网 > PDF目录376443 > X4C105 (Intersil Corporation) RTC Module With CPU Supervisor PDF资料下载

参数资料

| 型号: | X4C105 |

| 厂商: | Intersil Corporation |

| 元件分类: | CPU监测 |

| 英文描述: | RTC Module With CPU Supervisor |

| 中文描述: | 时钟模块CPU监控 |

| 文件页数: | 5/19页 |

| 文件大小: | 296K |

| 代理商: | X4C105 |

5

FN8124.0

March 18, 2005

SERIAL WRITE OPERATIONS

Byte Write

For a write operation, the device requires the slave

address byte and a word address byte. This gives the

master access to any one of the words in the array. After

receipt of the word address byte, the device responds

with an acknowledge, and awaits the next eight bits of

data. After receiving the 8 bits of the data byte, the device

again responds with an acknowledge. The master then

terminates the transfer by generating a stop condition, at

which time the device begins the internal write cycle to

the nonvolatile memory. During this internal write cycle,

the device inputs are disabled, so the device will not

respond to any requests from the master. The SDA out-

put is at high impedance. See Figure 5.

An attempted write to a protected block of memory will

suppress the acknowledge bit and the operation will

terminate.

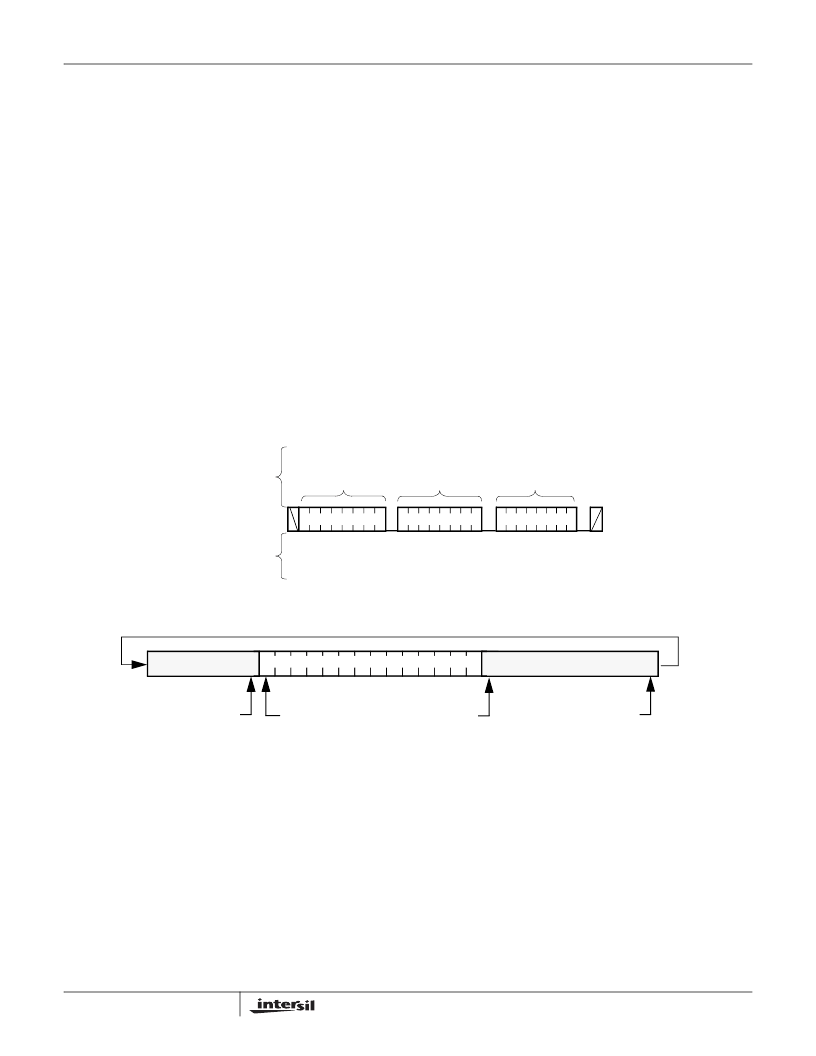

Page Write

The device is capable of a page write operation. It is

initiated in the same manner as the byte write opera-

tion; but instead of terminating the write cycle after the

first data byte is transferred, the master can transmit

an unlimited number of 8-bit bytes. After the receipt of

each byte, the device will respond with an acknowl-

edge, and the address is internally incremented by

one. The page address remains constant. When the

counter reaches the end of the page, it “rolls over” and

goes back to ‘0’ on the same page. This means that

the master can write 16 bytes to the page starting at

any location on that page. If the master begins writing

at location 10, and loads 12 bytes, then the first 5

bytes are written to locations 10 through 15, and the

last 7 bytes are written to locations 0 through 6. After-

wards, the address counter would point to location 7 of

the page that was just written. See Figure 6. If the master

supplies more than 16 bytes of data, then new data

over-writes the previous data, one byte at a time.

Figure 5. Byte Write Sequence

Figure 6. Writing 12 bytes to a 16-byte page starting at location 10.

S

t

a

r

t

S

t

o

p

Slave

Address

Byte

Address

Data

A

C

K

A

C

K

A

C

K

SDA Bus

Signals from

the Slave

Signals from

the Master

0

Address

n-1

Address

10

5 Bytes

7 Bytes

Address

= 6

Address Pointer

Ends Here

Addr = 7

X4C105

相关PDF资料 |

PDF描述 |

|---|---|

| X4C105V20I | RTC Module With CPU Supervisor |

| X5329V14Z-4.5A | RTC Module With CPU Supervisor |

| X5648P-4.5A | CAP 270PF 50V CERAMIC MONO 5% |

| X5648 | Thyristor Module |

| X5648P | RTC Module With CPU Supervisor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X4C105V20 | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

| X4C105V20-3A | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

| X4C105V20-3AT1 | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

| X4C105V20-3C7889 | 制造商:Intersil Corporation 功能描述: |

| X4C105V20I | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。