- 您现在的位置:买卖IC网 > PDF目录376443 > X4C105 (Intersil Corporation) RTC Module With CPU Supervisor PDF资料下载

参数资料

| 型号: | X4C105 |

| 厂商: | Intersil Corporation |

| 元件分类: | CPU监测 |

| 英文描述: | RTC Module With CPU Supervisor |

| 中文描述: | 时钟模块CPU监控 |

| 文件页数: | 8/19页 |

| 文件大小: | 296K |

| 代理商: | X4C105 |

8

FN8124.0

March 18, 2005

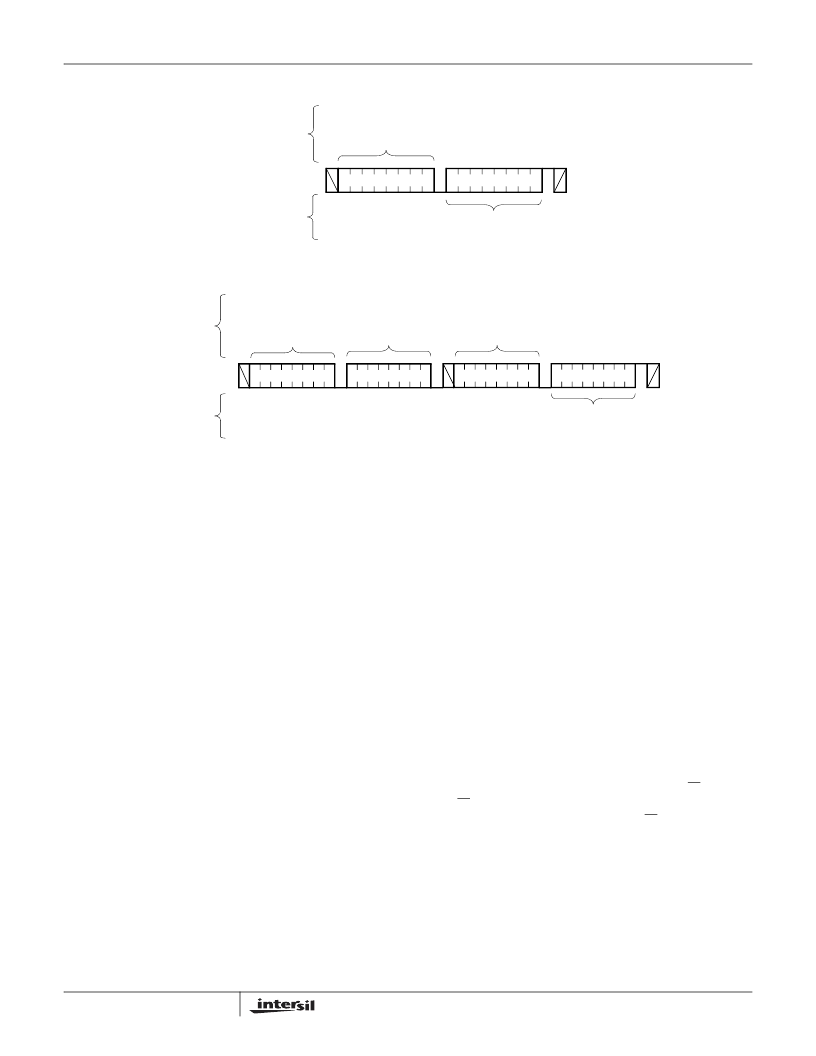

Figure 9. Current Address Read Sequence

Figure 10. Random Address Read Sequence

The device offers a similar operation, called “Set Cur-

rent Address,” where the device ends the transmission

and issues a stop instead of the second start, shown in

Figure 10. The device goes into standby mode after

the stop and all bus activity will be ignored until a start

is detected. This operation loads the new address into

the address counter. The next current address read

operation will then read from the newly loaded

address. This operation could be useful if the master

knows the next address it needs to read, but is not

ready for the data.

Sequential Read

Sequential reads can be initiated as either a current

address read or random address read. The first data

byte is transmitted as with the other modes; however,

the master now responds with an acknowledge, indicat-

ing it requires additional data. The device continues to

output data for each acknowledge received. The master

terminates the read operation by not responding with an

acknowledge and then issuing a stop condition.

The data output is sequential, with the data from address

n followed by the data from address n + 1. The address

counter for read operations increments through all page

and column addresses, allowing the entire memory con-

tents to be serially read during one operation. At the end

of the address space the counter “rolls over” to address

0000

H

and the device continues to output data for each

acknowledge received. Refer to Figure 11 for the

acknowledge and data transfer sequence.

SERIAL DEVICE ADDRESSING

Slave Address Byte

Following a start condition, the master must output a

slave address byte. This byte consists of several parts:

– a device type identifier that is always ‘1010’.

– two bits that provide the device select bits.

– one bit that becomes the MSB of the address.

– one bit of the slave command byte is a R/W bit. The

R/W bit of the slave address byte defines the opera-

tion to be performed. When the R/W bit is a one,

then a read operation is selected. A zero selects a

write operation. Refer to Figure 12.

S

t

a

r

t

S

t

o

p

Slave

Address

Data

A

C

K

SDA Bus

Signals from

the Slave

Signals from

the Master

1

0

Slave

Address

Byte

Address

A

C

K

A

C

K

S

t

a

r

t

S

t

o

p

Slave

Address

Data

A

C

K

1

S

t

a

r

t

SDA Bus

Signals from

the Slave

Signals from

the Master

X4C105

相关PDF资料 |

PDF描述 |

|---|---|

| X4C105V20I | RTC Module With CPU Supervisor |

| X5329V14Z-4.5A | RTC Module With CPU Supervisor |

| X5648P-4.5A | CAP 270PF 50V CERAMIC MONO 5% |

| X5648 | Thyristor Module |

| X5648P | RTC Module With CPU Supervisor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X4C105V20 | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

| X4C105V20-3A | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

| X4C105V20-3AT1 | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

| X4C105V20-3C7889 | 制造商:Intersil Corporation 功能描述: |

| X4C105V20I | 功能描述:IC SUPERVISOR NOVRAM/EE 20-TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:100 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:- 复位:低有效 复位超时:最小为 100 ms 电压 - 阀值:4.38V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-TSSOP(0.173",4.40mm 宽) 供应商设备封装:8-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。