参数资料

| 型号: | XA3S250E-4FTG256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 12/37页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 250K 456-FBGA |

| 标准包装: | 90 |

| 系列: | Spartan®-3E XA |

| LAB/CLB数: | 612 |

| 逻辑元件/单元数: | 5508 |

| RAM 位总计: | 221184 |

| 输入/输出数: | 172 |

| 门数: | 250000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

DS635 (v2.0) September 9, 2009

Product Specification

2

R

Key Feature Differences from Commercial XC Devices

AEC-Q100 device qualification and full production part

approval process (PPAP) documentation support

available in both extended temperature I- and

Q-Grades

Guaranteed to meet full electrical specification over the

TJ = –40°C to +125°C temperature range (Q-Grade)

XA Spartan-3E devices are available in the -4 speed

grade only.

PCI-66 is not supported in the XA Spartan-3E FPGA

product line.

The readback feature is not supported in the XA

Spartan-3E FPGA product line.

XA Spartan-3E devices are available in Step 1 only.

JTAG configuration frequency reduced from 30 MHz to

25 MHz.

Platform Flash is not supported within the XA family.

XA Spartan-3E devices are available in Pb-free

packaging only.

MultiBoot is not supported in XA versions of this

product.

The XA Spartan-3E device must be power cycled prior

to reconfiguration.

Architectural Overview

The XA Spartan-3E family architecture consists of five fun-

damental programmable functional elements:

Configurable Logic Blocks (CLBs) contain flexible

Look-Up Tables (LUTs) that implement logic plus

storage elements used as flip-flops or latches. CLBs

perform a wide variety of logical functions as well as

store data.

Input/Output Blocks (IOBs) control the flow of data

between the I/O pins and the internal logic of the

device. Each IOB supports bidirectional data flow plus

3-state operation. Supports a variety of signal

standards, including four high-performance differential

standards. Double Data-Rate (DDR) registers are

included.

Block RAM provides data storage in the form of

18-Kbit dual-port blocks.

Multiplier Blocks accept two 18-bit binary numbers as

inputs and calculate the product.

Digital Clock Manager (DCM) Blocks provide

self-calibrating, fully digital solutions for distributing,

delaying, multiplying, dividing, and phase-shifting clock

signals.

These elements are organized as shown in Figure 1. A ring

of IOBs surrounds a regular array of CLBs. Each device has

two columns of block RAM except for the XA3S100E, which

has one column. Each RAM column consists of several

18-Kbit RAM blocks. Each block RAM is associated with a

dedicated multiplier. The DCMs are positioned in the center

with two at the top and two at the bottom of the device. The

XA3S100E has only one DCM at the top and bottom, while

the XA3S1200E and XA3S1600E add two DCMs in the mid-

dle of the left and right sides.

The XA Spartan-3E family features a rich network of traces

that interconnect all five functional elements, transmitting

signals among them. Each functional element has an asso-

ciated switch matrix that permits multiple connections to the

routing.

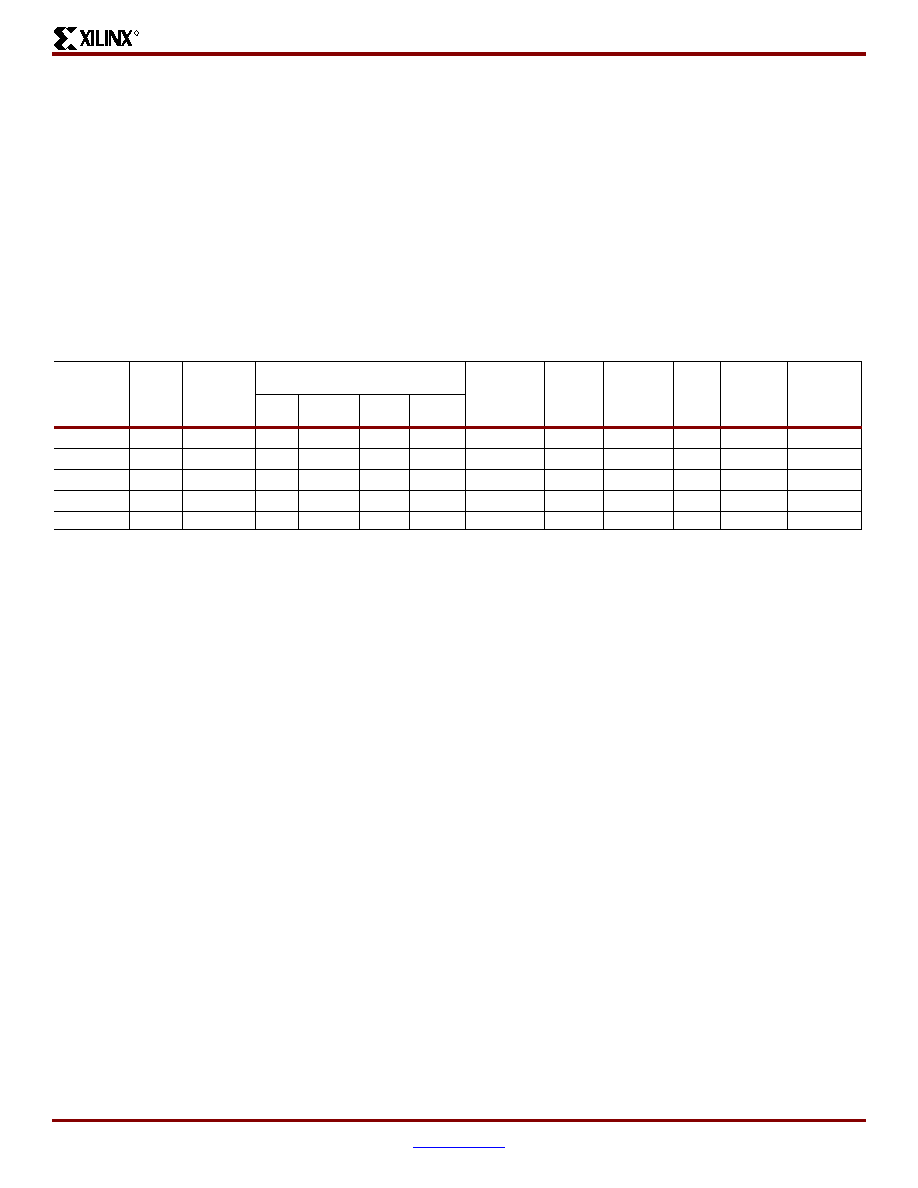

Table 1: Summary of XA Spartan-3E FPGA Attributes

Device

System

Gates

Equivalent

Logic

Cells

CLB Array

(One CLB = Four Slices)

Distributed

RAM bits(1)

Block

RAM

bits(1)

Dedicated

Multipliers

DCMs

Maximum

User I/O

Maximum

Differential

I/O Pairs

Rows Columns

Total

CLBs

Total

Slices

XA3S100E

100K

2,160

22

16

240

960

15K

72K

4

2

108

40

XA3S250E

250K

5,508

34

26

612

2,448

38K

216K

12

4

172

68

XA3S500E

500K

10,476

46

34

1,164

4,656

73K

360K

20

4

190

77

XA3S1200E

1200K

19,512

60

46

2,168

8,672

136K

504K

28

8

304

124

XA3S1600E

1600K

33,192

76

58

3,688

14,752

231K

648K

36

8

376

156

Notes:

1.

By convention, one Kb is equivalent to 1,024 bits.

相关PDF资料 |

PDF描述 |

|---|---|

| XC2S200E-6PQG208C | IC SPARTAN-IIE FPGA 200K 208PQFP |

| XC2S200E-6PQ208C | IC FPGA 1.8V 1176 CLB'S 208-PQFP |

| 747275-4 | CONN D-SUB STRAIN RELIEF 9POS |

| XC3S700A-5FTG256C | IC FPGA SPARTAN-3A 256K 256FTBGA |

| XA3S400-4PQG208Q | IC FPGA SPARTAN-3 400K 208-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA3S250E-4FTG256Q | 功能描述:IC FPGA SPARTAN-3E 250K 456-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4PQG208I | 功能描述:IC FPGA SPARTAN-3E 250K 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4PQG208Q | 功能描述:IC FPGA SPARTAN-3E 250K 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4TQG144I | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4TQG144Q | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。