- 您现在的位置:买卖IC网 > PDF目录277726 > XA3S250E-4PQG208I (XILINX INC) FPGA, 612 CLBS, 250000 GATES, 572 MHz, PQFP208 PDF资料下载

参数资料

| 型号: | XA3S250E-4PQG208I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 612 CLBS, 250000 GATES, 572 MHz, PQFP208 |

| 封装: | LEAD FREE, PLASTIC, QFP-208 |

| 文件页数: | 11/37页 |

| 文件大小: | 717K |

| 代理商: | XA3S250E-4PQG208I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

DS635 (v2.0) September 9, 2009

Product Specification

19

R

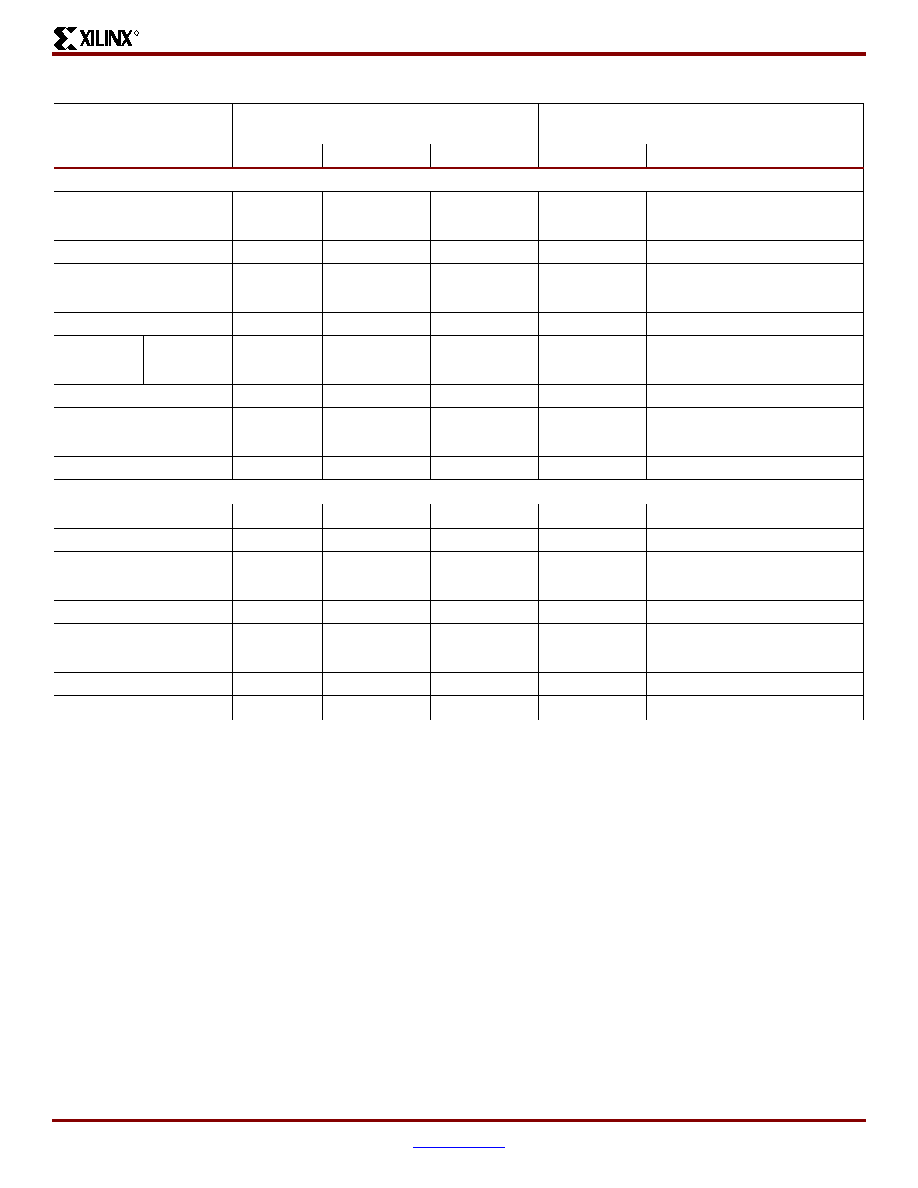

Table 19: Test Methods for Timing Measurement at I/Os

Signal Standard

(IOSTANDARD)

Inputs

Outputs

Inputs and

Outputs

VREF (V)

VL (V)

VH (V)

RT (Ω)VT (V)

VM (V)

Single-Ended

LVTTL

-

03.3

1M

01.4

LVCMOS33

-

0

3.3

1M

0

1.65

LVCMOS25

-

0

2.5

1M

0

1.25

LVCMOS18

-

0

1.8

1M

0

0.9

LVCMOS15

-

0

1.5

1M

0

0.75

LVCMOS12

-

0

1.2

1M

0

0.6

PCI33_3

Rising

-

Note 3

25

0

0.94

Falling

25

3.3

2.03

HSTL_I_18

0.9

VREF – 0.5

VREF + 0.5

50

0.9

VREF

HSTL_III_18

1.1

VREF – 0.5

VREF + 0.5

50

1.8

VREF

SSTL18_I

0.9

VREF – 0.5

VREF + 0.5

50

0.9

VREF

SSTL2_I

1.25

VREF – 0.75

VREF + 0.75

50

1.25

VREF

Differential

LVDS_25

-

VICM – 0.125

VICM + 0.125

50

1.2

VICM

BLVDS_25

-

VICM – 0.125

VICM + 0.125

1M

0

VICM

MINI_LVDS_25

-

VICM – 0.125

VICM + 0.125

50

1.2

VICM

LVPECL_25

-

VICM – 0.3

VICM + 0.3

1M

0

VICM

RSDS_25

-

VICM – 0.1

VICM + 0.1

50

1.2

VICM

DIFF_HSTL_I_18

-

VREF – 0.5

VREF + 0.5

50

0.9

VICM

DIFF_HSTL_III_18

-

VREF – 0.5

VREF + 0.5

50

1.8

VICM

DIFF_SSTL18_I

-

VREF – 0.5

VREF + 0.5

50

0.9

VICM

DIFF_SSTL2_I

-

VREF – 0.5

VREF + 0.5

50

1.25

VICM

Notes:

1.

Descriptions of the relevant symbols are as follows:

VREF – The reference voltage for setting the input switching threshold

VICM – The common mode input voltage

VM – Voltage of measurement point on signal transition

VL – Low-level test voltage at Input pin

VH – High-level test voltage at Input pin

RT – Effective termination resistance, which takes on a value of 1MΩ when no parallel termination is required

VT – Termination voltage

2.

The load capacitance (CL) at the Output pin is 0 pF for all signal standards.

3.

According to the PCI specification.

相关PDF资料 |

PDF描述 |

|---|---|

| XA3S250E-4TQG144I | FPGA, 612 CLBS, 250000 GATES, 572 MHz, PQFP144 |

| XD-14596F4-364W | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

| XD-14596F4-372Q | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

| XD-14596F4-432 | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

| XD-14596F4-462L | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA3S250E-4PQG208Q | 功能描述:IC FPGA SPARTAN-3E 250K 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4TQG144I | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4TQG144Q | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4VQG100I | 功能描述:IC FPGA SPARTAN-3E 250K 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4VQG100Q | 功能描述:IC FPGA SPARTAN-3E 250K 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。