- 您现在的位置:买卖IC网 > PDF目录277726 > XA3S250E-4PQG208I (XILINX INC) FPGA, 612 CLBS, 250000 GATES, 572 MHz, PQFP208 PDF资料下载

参数资料

| 型号: | XA3S250E-4PQG208I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 612 CLBS, 250000 GATES, 572 MHz, PQFP208 |

| 封装: | LEAD FREE, PLASTIC, QFP-208 |

| 文件页数: | 3/37页 |

| 文件大小: | 717K |

| 代理商: | XA3S250E-4PQG208I |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

DS635 (v2.0) September 9, 2009

Product Specification

11

R

Single-Ended I/O Standards

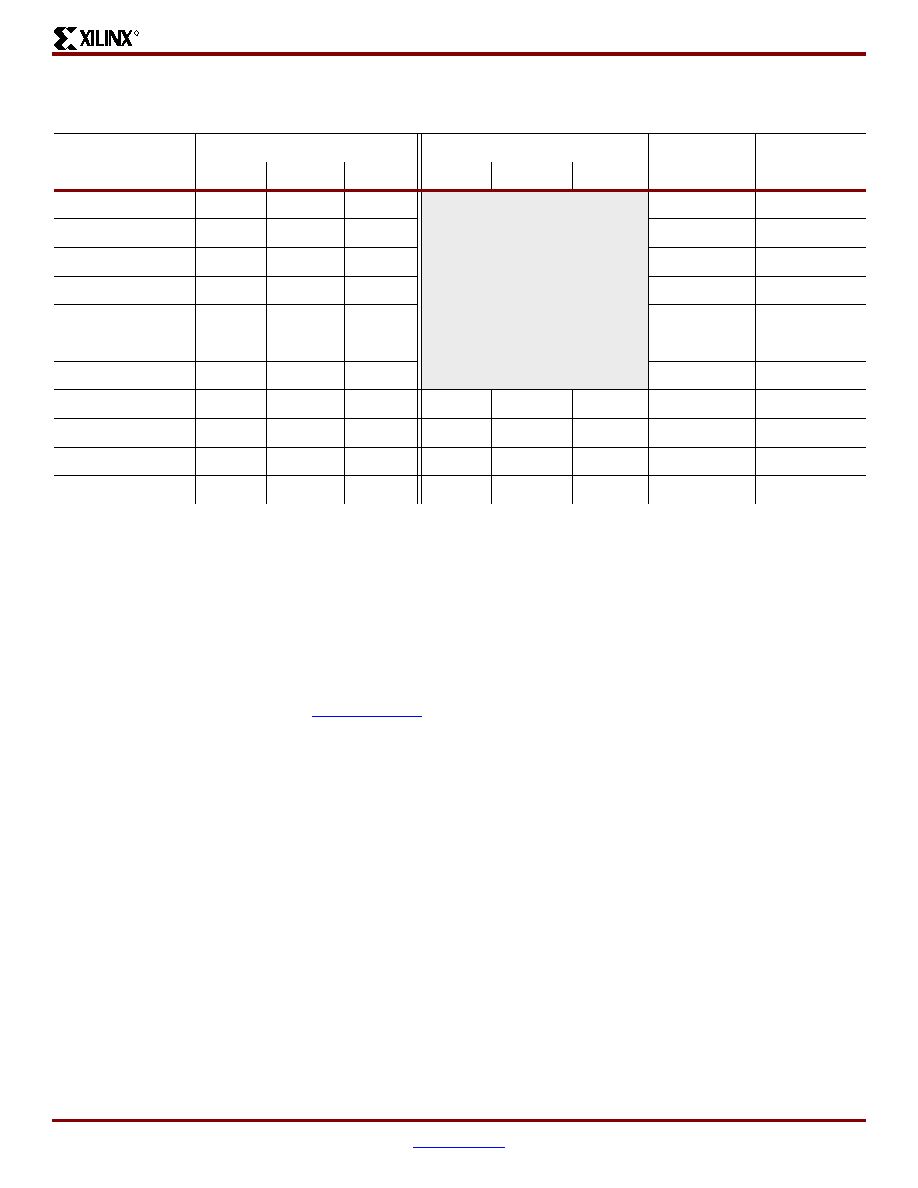

Table 9: Recommended Operating Conditions for User I/Os Using Single-Ended Standards

IOSTANDARD

Attribute

VCCO for Drivers(2)

VREF

VIL

VIH

Min (V)

Nom (V)

Max (V)

Min (V)

Nom (V)

Max (V)

Min (V)

LVTTL

3.0

3.3

3.465

VREF is not used for

these I/O standards

0.8

2.0

LVCMOS33(4)

3.0

3.3

3.465

0.8

2.0

LVCMOS25(4,5)

2.3

2.5

2.7

0.7

1.7

LVCMOS18

1.65

1.8

1.95

0.4

0.8

LVCMOS15

1.4

1.5

1.6

0.4

0.8

LVCMOS12

1.1

1.2

1.3

0.4

0.7

PCI33_3

3.0

3.3

3.465

0.3 * VCCO

0.5 * VCCO

HSTL_I_18

1.7

1.8

1.9

0.8

0.9

1.1

VREF - 0.1

VREF + 0.1

HSTL_III_18

1.7

1.8

1.9

-

1.1

-

VREF - 0.1

VREF + 0.1

SSTL18_I

1.7

1.8

1.9

0.833

0.900

0.969

VREF - 0.125

VREF + 0.125

SSTL2_I

2.3

2.5

2.7

1.15

1.25

1.35

VREF - 0.125

VREF + 0.125

Notes:

1.

Descriptions of the symbols used in this table are as follows:

VCCO – the supply voltage for output drivers

VREF – the reference voltage for setting the input switching threshold

VIL – the input voltage that indicates a Low logic level

VIH – the input voltage that indicates a High logic level

2.

The VCCO rails supply only output drivers, not input circuits.

3.

For device operation, the maximum signal voltage (VIH max) may be as high as VIN max. See Table 72 in DS312.

4.

There is approximately 100 mV of hysteresis on inputs using LVCMOS33 and LVCMOS25 I/O standards.

5.

All Dedicated pins (PROG_B, DONE, TCK, TDI, TDO, and TMS) use the LVCMOS25 standard and draw power from the VCCAUX rail (2.5V).

The Dual-Purpose configuration pins use the LVCMOS standard before the User mode. When using these pins as part of a standard 2.5V

configuration interface, apply 2.5V to the VCCO lines of Banks 0, 1, and 2 at power-on as well as throughout configuration.

6.

For information on PCI IP solutions, see www.xilinx.com/pci.

相关PDF资料 |

PDF描述 |

|---|---|

| XA3S250E-4TQG144I | FPGA, 612 CLBS, 250000 GATES, 572 MHz, PQFP144 |

| XD-14596F4-364W | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

| XD-14596F4-372Q | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

| XD-14596F4-432 | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

| XD-14596F4-462L | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CDFP36 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA3S250E-4PQG208Q | 功能描述:IC FPGA SPARTAN-3E 250K 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4TQG144I | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4TQG144Q | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4VQG100I | 功能描述:IC FPGA SPARTAN-3E 250K 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S250E-4VQG100Q | 功能描述:IC FPGA SPARTAN-3E 250K 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。