- 您现在的位置:买卖IC网 > PDF目录300144 > XC3020A7PC68I (Xilinx, Inc.) IC-SMD-FPGA PDF资料下载

参数资料

| 型号: | XC3020A7PC68I |

| 厂商: | Xilinx, Inc. |

| 英文描述: | IC-SMD-FPGA |

| 中文描述: | 集成电路贴片的FPGA |

| 文件页数: | 10/76页 |

| 文件大小: | 731K |

| 代理商: | XC3020A7PC68I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

R

XC3000 Series Field Programmable Gate Arrays

7-20

November 9, 1998 (Version 3.1)

A re-program is initiated.when a configured XC3000 series

device senses a High-to-Low transition and subsequent >6

s Low level on the DONE/PROG package pin, or, if this

pin is externally held permanently Low, a High-to-Low tran-

sition and subsequent >6

s Low time on the RESET pack-

age pin.

The device returns to the Clear state where the configura-

tion memory is cleared and mode lines re-sampled, as for

an aborted configuration. The complete configuration pro-

gram is cleared and loaded during each configuration pro-

gram cycle.

Length count control allows a system of multiple Field Pro-

grammable Gate Arrays, of assorted sizes, to begin opera-

tion in a synchronized fashion. The configuration program

generated by the development system begins with a pre-

amble of 111111110010 followed by a 24-bit length count

representing the total number of configuration clocks

needed to complete loading of the configuration pro-

gram(s). The data framing is shown in Figure 21. All

FPGAs connected in series read and shift preamble and

length count in on positive and out on negative configura-

tion clock edges. A device which has received the pream-

ble and length count then presents a High Data Out until it

has intercepted the appropriate number of data frames.

When the configuration program memory of an FPGA is full

and the length count does not yet compare, the device

shifts any additional data through, as it did for preamble

and length count. When the FPGA configuration memory is

full and the length count compares, the device will execute

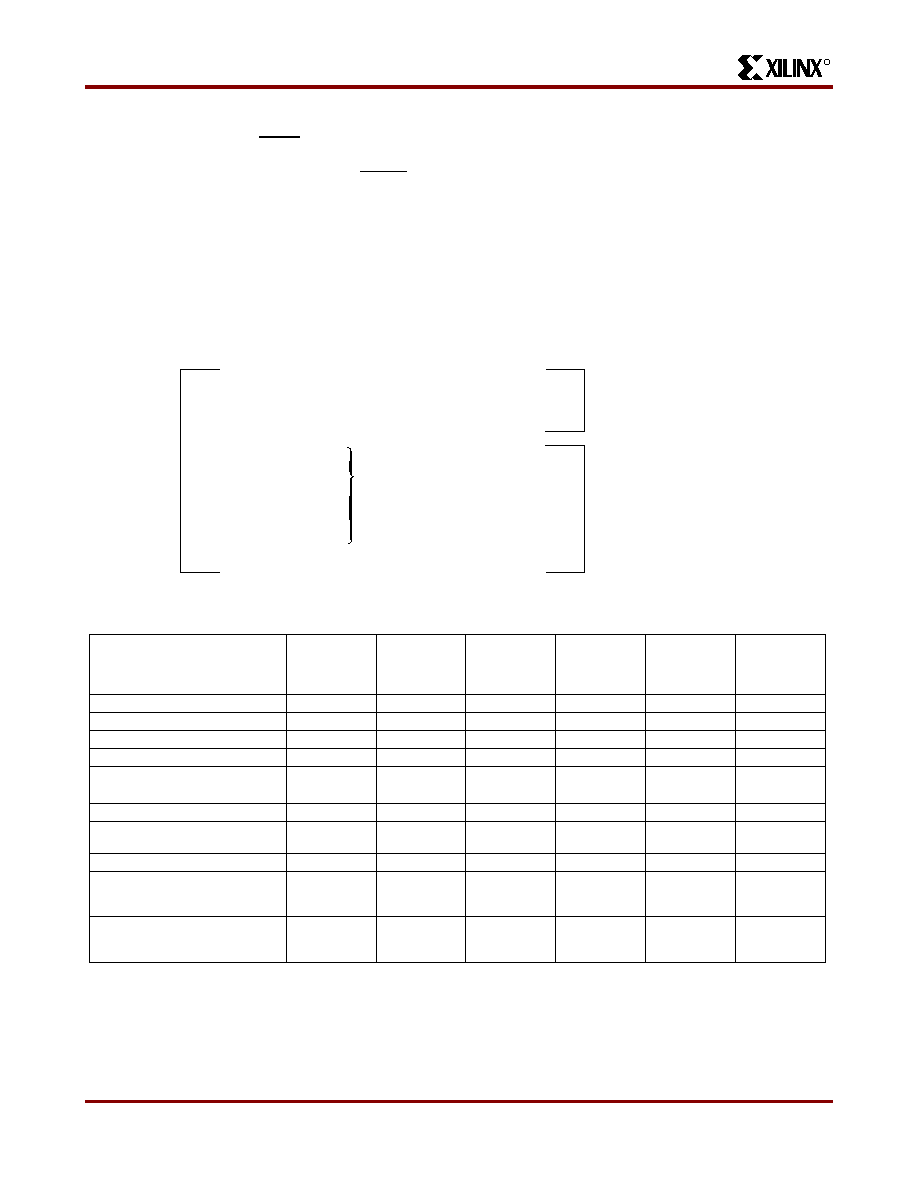

11111111

0010

< 24-Bit Length Count >

1111

0 <Data Frame # 001 > 111

0 <Data Frame # 002 > 111

0 <Data Frame # 003 > 111

.

0 <Data Frame # 196 > 111

0 <Data Frame # 197 > 111

1111

—Dummy Bits*

—Preamble Code

—Configuration Program Length

—Dummy Bits (4 Bits Minimum)

For XC3120

197 Configuration Data Frames

(Each Frame Consists of:

A Start Bit (0)

A 71-Bit Data Field

Three Stop Bits

Postamble Code (4 Bits Minimum)

Header

Program Data

Repeated for Each Logic

Cell Array in a Daisy Chain

*The LCA Device Require Four Dummy Bits Min; Software Generates Eight Dummy Bits

X5300_01

Figure 21: Internal Configuration Data Structure for an FPGA. This shows the preamble, length count and data

frames generated by the Development System.

The Length Count produced by the program = [(40-bit preamble + sum of program data + 1 per daisy chain device)

rounded up to multiple of 8] – (2

≤ K ≤ 4) where K is a function of DONE and RESET timing selected. An additional 8 is

added if roundup increment is less than K. K additional clocks are needed to complete start-up after length count is

reached.

Device

XC3020A

XC3020L

XC3120A

XC3030A

XC3030L

XC3130A

XC3042A

XC3042L

XC3142A

XC3142L

XC3064A

XC3064L

XC3164A

XC3090A

XC3090L

XC3190A

XC3190L

XC3195A

Gates

1,000 to 1,500

1,500 to 2,000

2,000 to 3,000

3,500 to 4,500

5,000 to 6,000

6,500 to 7,500

CLBs

64

100

144

224

320

484

Row x Col

(8 x 8)

(10 x 10)

(12 x 12)

(16 x 14)

(20 x 16)

(22 x 22)

IOBs

64

80

96

120

144

176

Flip-flops

256

360

480

688

928

1,320

Horizontal Longlines

16

20

24

32

40

44

TBUFs/Horizontal LL

9

11

13

15

17

23

Bits per Frame

(including1 start and 3 stop bits)

75

92

108

140

172

188

Frames

197

241

285

329

373

505

Program Data =

Bits x Frames + 4 bits

(excludes header)

14,779

22,176

30,784

46,064

64,160

94,944

PROM size (bits) =

Program Data

+ 40-bit Header

14,819

22,216

30,824

46,104

64,200

94,984

相关PDF资料 |

PDF描述 |

|---|---|

| XC3064A-6PQ160C | Field Programmable Gate Array (FPGA) |

| XC3064A-7PQ160I | Field Programmable Gate Array (FPGA) |

| XC4000XLASERIES | Field Programmable Gate Arrays |

| XC4013E-1CB240M | Programmable Gate Arrays |

| XC4013E-1HG240C | Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3020A-7PC68I | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3020A-7PC84C | 功能描述:IC LOGIC CL ARRAY 2000GAT 84PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:XC3000A/L 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC3020A-7PC84C0100 | 制造商:Xilinx 功能描述: |

| XC3020A-7PC84I | 制造商:Xilinx 功能描述: |

| XC3020A-7PCG68C | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。