参数资料

| 型号: | XC3S250E-4PQG208I |

| 厂商: | Xilinx Inc |

| 文件页数: | 178/227页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 250K 208-PQFP |

| 标准包装: | 24 |

| 系列: | Spartan®-3E |

| LAB/CLB数: | 612 |

| 逻辑元件/单元数: | 5508 |

| RAM 位总计: | 221184 |

| 输入/输出数: | 158 |

| 门数: | 250000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页当前第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页

Spartan-3E FPGA Family: Functional Description

DS312 (v4.1) July 19, 2013

Product Specification

54

The CLKFX_DIVIDE is an integer ranging from 1 to 32,

inclusive and forms the denominator in Equation 1. For

example, if CLKFX_MULTIPLY = 5 and CLKFX_DIVIDE = 3,

the frequency of the output clock signal is 5/3 that of the

input clock signal. These attributes and their acceptable

ranges are described in Table 34.

Any combination of integer values can be assigned to the

CLKFX_MULTIPLY and CLKFX_DIVIDE attributes,

provided that two conditions are met:

1.

The two values fall within their corresponding ranges,

as specified in Table 34.

2.

falls within the DCM’s operating frequency

specifications (see Table 107 in Module 3).

DFS With or Without the DLL

Although the CLKIN input is shared with both units, the DFS

unit functions with or separately from the DLL unit. Separate

from the DLL, the DFS generates an output frequency from

the CLKIN frequency according to the respective

CLKFX_MULTIPLY and CLKFX_DIVIDE values. Frequency

synthesis does not require a feedback loop. Furthermore,

without the DLL, the DFS unit supports a broader operating

frequency range.

With the DLL, the DFS unit operates as described above,

only with the additional benefit of eliminating the clock

distribution delay. In this case, a feedback loop from the

CLK0 or CLK2X output to the CLKFB input must be present.

When operating with the DLL unit, the DFS’s CLKFX and

CLKFX180 outputs are phase-aligned with the CLKIN input

every CLKFX_DIVIDE cycles of CLKIN and every

CLKFX_MULTIPLY cycles of CLKFX. For example, when

CLKFX_MULTIPLY = 5 and CLKFX_DIVIDE = 3, the input

and output clock edges coincide every three CLKIN input

periods, which is equivalent in time to five CLKFX output

periods.

Smaller CLKFX_MULTIPLY and CLKFX_DIVIDE values

result in faster lock times. Therefore, CLKFX_MULTIPLY

and CLKFX_DIVIDE must be factored to reduce their values

wherever possible. For example, given CLKFX_MULTIPLY

= 9 and CLKFX_DIVIDE = 6, removing a factor of three

yields CLKFX_MULTIPLY = 3 and CLKFX_DIVIDE = 2.

While both value-pairs result in the multiplication of clock

frequency by 3/2, the latter value-pair enables the DLL to

lock more quickly.

Phase Shifter (PS)

The DCM provides two approaches to controlling the phase

of a DCM clock output signal relative to the CLKIN signal:

First, eight of the nine DCM clock outputs

– CLK0, CLK90,

CLK180, CLK270, CLK2X, CLK2X180, CLKFX, and

CLKFX180

– provide either quadrant or half-period phase

shifting of the input clock.

Second, the PS unit provides additional fine phase shift

control of all nine DCM outputs. The PS unit accomplishes

this by introducing a “fine phase shift” delay (TPS) between

the CLKFB and CLKIN signals inside the DLL unit. In FIXED

phase shift mode, the fine phase shift is specified at design

time with a resolution down to 1/256th of a CLKIN cycle or

one delay step (DCM_DELAY_STEP), whichever is greater.

This fine phase shift value is relative to the coarser quadrant

or half-period phase shift of the DCM clock output. When

used, the PS unit shifts the phase of all nine DCM clock

output signals.

Enabling Phase Shifting and Selecting an Operat-

ing Mode

The CLKOUT_PHASE_SHIFT attribute controls the PS unit

for the specific DCM instantiation. As described in Table 35,

this attribute has three possible values: NONE, FIXED, and

VARIABLE. When CLKOUT_PHASE_SHIFT = NONE, the

PS unit is disabled and the DCM output clocks are

phase-aligned to the CLKIN input via the CLKFB feedback

path. Figure 44a shows this case.

The PS unit is enabled when the CLKOUT_PHASE_SHIFT

attribute is set to FIXED or VARIABLE modes. These two

modes are described in the sections that follow.

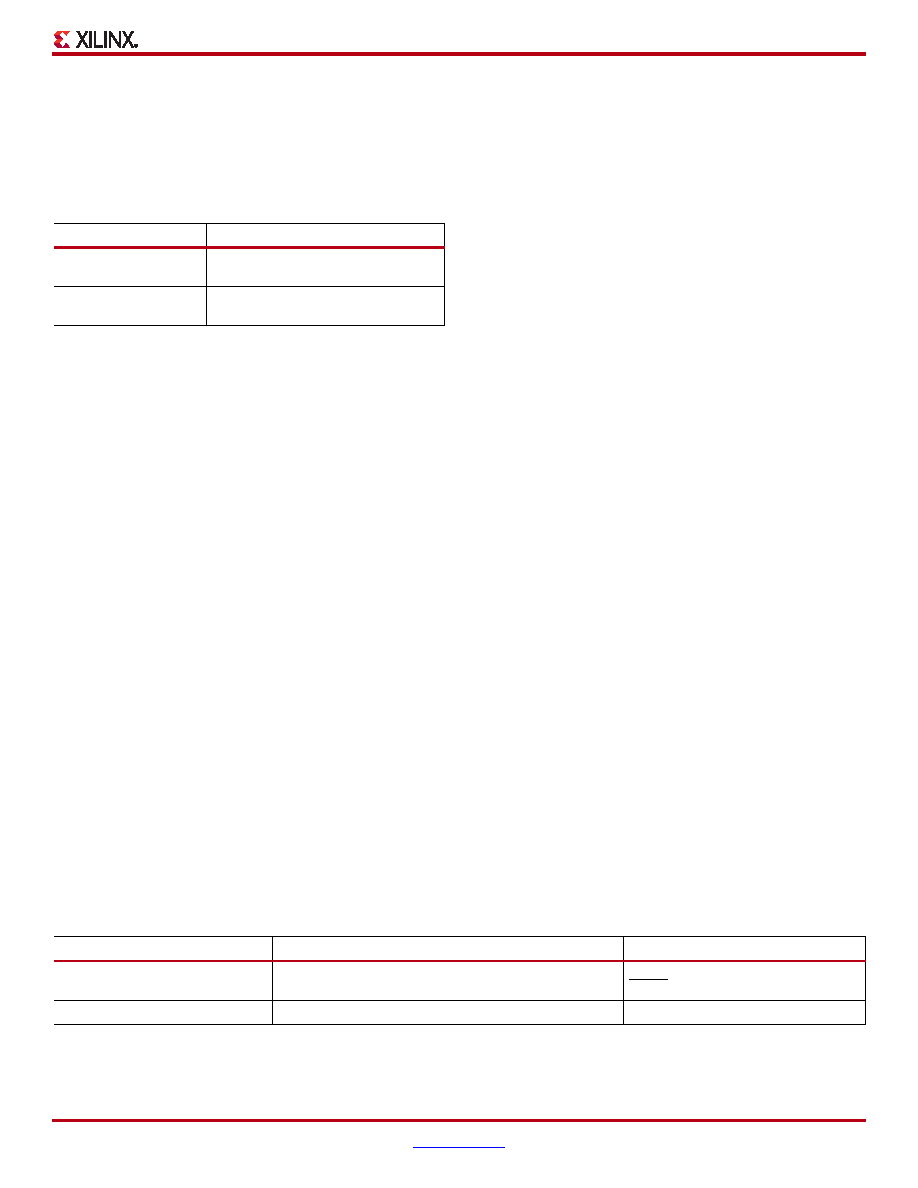

Table 34: DFS Attributes

Attribute

Description

Values

CLKFX_MULTIPLY

Frequency multiplier

constant

Integer from 2

to 32, inclusive

CLKFX_DIVIDE

Frequency divisor

constant

Integer from 1

to 32, inclusive

Table 35: PS Attributes

Attribute

Description

Values

CLKOUT_PHASE_SHIFT

Disables the PS component or chooses between Fixed

Phase and Variable Phase modes.

NONE, FIXED, VARIABLE

PHASE_SHIFT

Determines size and direction of initial fine phase shift.

Integers from –255 to +255

相关PDF资料 |

PDF描述 |

|---|---|

| AYM43DRST-S288 | CONN EDGECARD 86POS .156 EXTEND |

| XC3S200A-5FGG320C | IC SPARTAN-3A FPGA 200K 320-FBGA |

| 93LC76CT-I/ST | IC EEPROM 8KBIT 3MHZ 8TSSOP |

| EHHD15MM | CONN DSUB 15PIN MALE-MALE |

| ASM43DRST-S288 | CONN EDGECARD 86POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3S250E-4TQ144C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 250K GATES 5508 CELLS 572MHZ 90NM 1.2V 144TQ - Trays |

| XC3S250E-4TQ144I | 功能描述:IC FPGA SPARTAN 3E 144TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S250E-4TQG144C | 功能描述:IC SPARTAN-3E FPGA 250K 144TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| XC3S250E-4TQG144I | 功能描述:IC FPGA SPARTAN-3E 250K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S250E-4VQ100C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 250K GATES 5508 CELLS 572MHZ 90NM 1.2V 100VT - Trays |

发布紧急采购,3分钟左右您将得到回复。