- 您现在的位置:买卖IC网 > PDF目录225572 > XC4VFX100-11FF1152I (XILINX INC) FPGA, 10544 CLBS, 1181 MHz, PBGA1152 PDF资料下载

参数资料

| 型号: | XC4VFX100-11FF1152I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| 封装: | FBGA-1152 |

| 文件页数: | 53/58页 |

| 文件大小: | 1863K |

| 代理商: | XC4VFX100-11FF1152I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

57

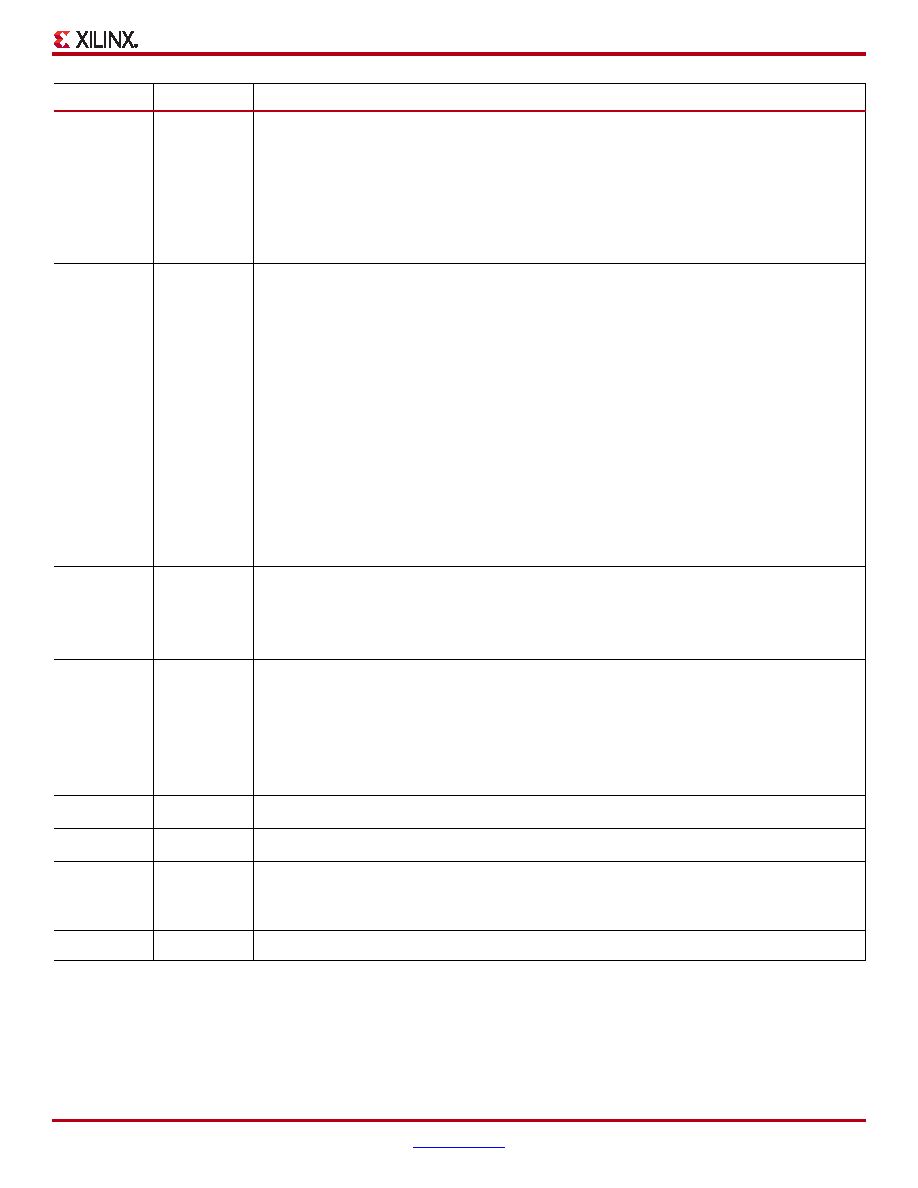

09/28/07

3.0

SPEED SPECIFICATION version for this data sheet release: v1.67.

Promoted data sheet to Production status.

Table 14: Moved XC4VFX140, all speed grades, from Advance to Production status.

Table 59: Added/updated all Global Clock Tree Skew values. Qualified Note (2) by

adding “vertical”.

Table 60: Added Package Skew values for XC4VFX40, XC4VFX100, and XC4VFX140.

Table 63: Added JTAG ID code for XC4VFX140.

12/11/07

3.1

SPEED SPECIFICATION version for this data sheet release: v1.68.

Added new copyright notice and legal disclaimer section.

Table 13: Removed table note references to XAPP700, XAPP704, and XAPP705

(obsolete). Renumbered table notes.

Table 15: Added new Note 1, renumbered subsequent table notes.

Table 30: Removed table rows for LVPECL_33, LVDS_33, and LVDSEXT_33.

Table 31: For LVDS Extended Mode 2.5V, corrected I/O Standard Attribute to

LVDSEXT_25.

Section Production Stepping, page 51: Advised that current stepping level is reported

by the ISE tool in the PAR report.

04/10/08

3.2

SPEED SPECIFICATION version for this data sheet release: v1.68.

Table 28, page 22: Re-inserted table.

Table 43, page 36: Updated Symbol names for the DRP entries.

Table 63, page 51: Revised code for XC4VFX40 package to 0.

06/06/08

3.3

SPEED SPECIFICATION version for this data sheet release: v1.68.

Table 3, page 3: In Note (2), clarified differences between settings for typical and

maximum ICC numbers.

on the speed grade. Removed TPHASE.

Table 35, page 29: Reorganized according to IDELAYCTRL and IDELAY.

11/26/08

3.4

06/16/09

3.5

08/13/09

3.6

Table 3, page 3: Updated Note 1.

Table 45, page 38: Added Note 6 reference to and updated descriptions of

CLKIN_FREQ_DLL_HF_MS_MIN and CLKIN_FREQ_FX_HF_MS_MAX.

09/09/09

3.7

Table 7, page 8: Added “LVCMOS” to Notes 3 and 4.

Date

Version

Revisions

相关PDF资料 |

PDF描述 |

|---|---|

| XC4VFX100-11FF1517I | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

| XC4VFX100-10FFG1152I | FPGA, 10544 CLBS, 1028 MHz, PBGA1152 |

| XC4VFX100-10FFG1517I | FPGA, 10544 CLBS, 1028 MHz, PBGA1517 |

| XC4VFX100-11FFG1152I | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| XC4VFX100-11FFG1517I | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VFX100-11FF1517C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 94896 CELLS 90NM 1.2V 1517FCBGA - Trays |

| XC4VFX100-11FF1517CES4 | 制造商:Xilinx 功能描述: |

| XC4VFX100-11FF1517CES4S | 制造商:Xilinx 功能描述: |

| XC4VFX100-11FF1517I | 功能描述:IC FPGA VIRTEX-4FX 1517FFBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC4VFX100-11FF1517IES4 | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。