参数资料

| 型号: | XR16C2850IM-F |

| 厂商: | Exar Corporation |

| 文件页数: | 22/51页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 128B DUAL 48TQFP |

| 标准包装: | 250 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 128 字节 |

| 规程: | RS232,RS485 |

| 电源电压: | 2.97 V ~ 5.5 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 托盘 |

| 其它名称: | 1016-1275 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页

xr

XR16C2850

REV. 2.1.3

2.97V TO 5.5V DUAL UART WITH 128-BYTE FIFOS

29

LCR[5]: TX and RX Parity Select

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5 = logic 0, parity is not forced (default).

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit is forced to a logical 1 for the transmit and receive

data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit is forced to a logical 0 for the transmit and receive

data.

LCR[6]: Transmit Break Enable

When enabled, the Break control bit causes a break condition to be transmitted (the TX output is forced to a

“space’, LOW, state). This condition remains, until disabled by setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition (default).

Logic 1 = Forces the transmitter output (TX) to a “space”, LOW, for alerting the remote receiver of a line

break condition.

LCR[7]: Baud Rate Divisors Enable

Baud rate generator divisor (DLL/DLM) enable.

Logic 0 = Data registers are selected (default).

Logic 1 = Divisor latch registers are selected.

4.7

Modem Control Register (MCR) or General Purpose Outputs Control - Read/Write

The MCR register is used for controlling the serial/modem interface signals or general purpose inputs/outputs.

MCR[0]: DTR# Output

The DTR# pin is a modem control output. If the modem interface is not used, this output may be used as a

general purpose output.

Logic 0 = Force DTR# output HIGH (default).

Logic 1 = Force DTR# output LOW.

MCR[1]: RTS# Output

The RTS# pin is a modem control output and may be used for automatic hardware flow control enabled by

EFR bit-6. The RTS# output must be asserted before the auto RTS can take effect. If the modem interface is

not used, this output may be used as a general purpose output.

Logic 0 = Force RTS# output HIGH (default).

Logic 1 = Force RTS# output LOW. If auto RTS flow control is enabled, it will take effect after this bit has

been set.

MCR[2]: Reserved

OP1# is not available as an output pin on the 2850. But it is available for use during Internal Loopback Mode.

In the Loopback Mode, this bit is used to write the state of the modem RI# interface signal.

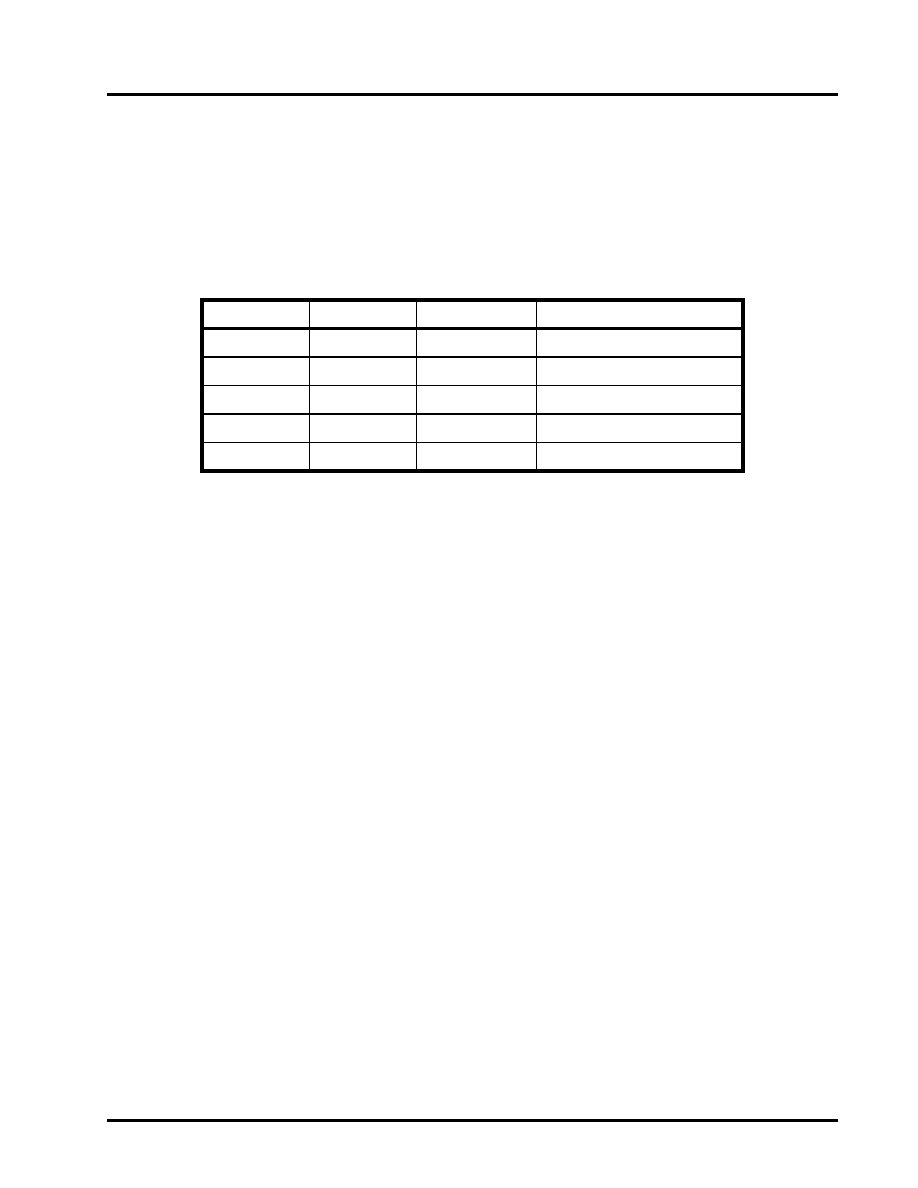

TABLE 11: PARITY SELECTION

LCR BIT-5

LCR BIT-4

LCR BIT-3

PARITY SELECTION

X

0

No parity

0

1

Odd parity

0

1

Even parity

1

0

1

Force parity to mark, “1”

1

Forced parity to space, “0”

相关PDF资料 |

PDF描述 |

|---|---|

| XR16C2852IJ-F | IC UART FIFO 128B 44PLCC |

| XR16C850IMTR-F | IC UART FIFO 128B 48TQFP |

| XR16C854IQ-F | IC UART FIFO 128B QUAD 100QFP |

| XR16C864IQ-F | IC UART FIFO 128B QUAD 100QFP |

| XR16L2450IJ-F | IC UART FIFO 1B DUAL 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16C2850IMTR-F | 制造商:Exar Corporation 功能描述:XR16C2850IMTR-F |

| XR16C2850IP | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL UART WITH 128-byte FIFO’s AND RS-485 HALF DUPLEX CONTROL |

| XR16C2850IP40 | 制造商:EXAR 制造商全称:EXAR 功能描述:3.3V AND 5V DUART WITH 128-BYTE FIFO |

| XR16C2852 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUAL UART WITH 128-BYTE FIFOS |

| XR16C2852_05 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUAL UART WITH 128-BYTE FIFOS |

发布紧急采购,3分钟左右您将得到回复。