- 您现在的位置:买卖IC网 > PDF目录67334 > 5962-9169101M3A (CRYSTAL SEMICONDUCTOR CORP) 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC28 PDF资料下载

参数资料

| 型号: | 5962-9169101M3A |

| 厂商: | CRYSTAL SEMICONDUCTOR CORP |

| 元件分类: | ADC |

| 英文描述: | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC28 |

| 封装: | LCC-28 |

| 文件页数: | 4/48页 |

| 文件大小: | 647K |

| 代理商: | 5962-9169101M3A |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

GENERAL DESCRIPTION

The CS5101A and CS5102A are 2-channel, 16-

bit A/D converters. The devices include an

inherent sample/hold and an on-chip analog

switch for 2-channel operation. Both channels

can thus be sampled and converted at rates up to

50 k Hz each (CS5101A) or 10 kHz each

(CS5102A). Alternatively, each of the devices

can be operated as a single channel ADC operat-

ing at 100 kHz (CS5101A) or 20 kHz

(CS5102A).

Both the CS5101A and CS5102A can be config-

ured to accept either unipolar or bipolar input

ranges, and data is output serially in either binary

or 2’s complement coding. The devices can be

configured in 3 different output modes, as well as

an internal, synchronous loopback mode. The

CS5101A and CS5102A prov ide co arse

charge/fine charge control, to allow accurate

tracking of high-slew signals.

THEORY OF OPERATION

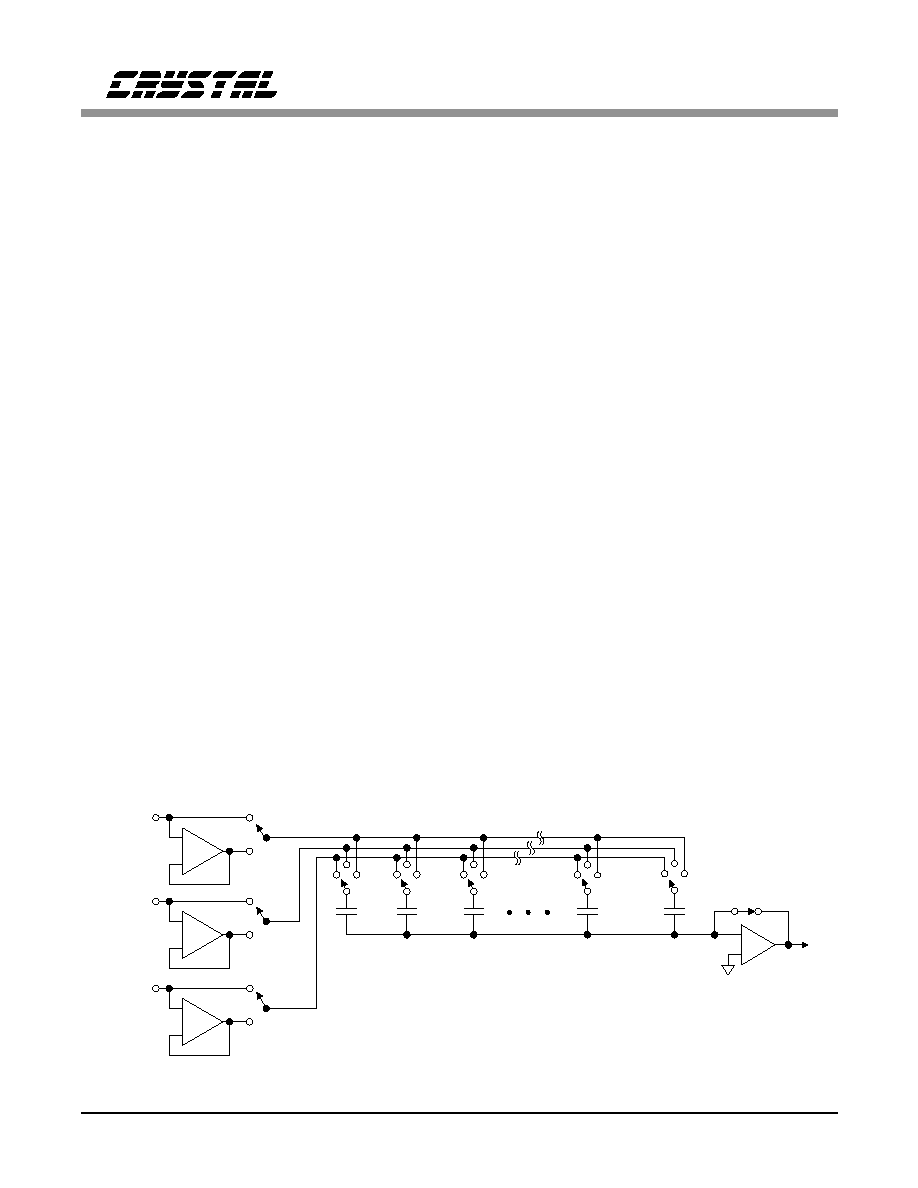

The CS5101A and CS5102A implement the suc-

cessive approximation algorithm using a charge

redistribution architecture. Instead of the tradi-

tional resistor network, the DAC is an array of

binary-weighted capacitors. All capacitors in the

array share a common node at the comparator’s

input. As shown in Figure 1, their other terminals

are capable of being connected to AGND, VREF,

or AIN (1 or 2). When the device is not calibrat-

ing or converting, all capacitors are tied to AIN.

Switch S1 is closed and the charge on the array,

tracks the input signal.

When the conversion command is issued, switch

S1 opens. This traps the charge on the compara-

tor side of the capacitor array and creates a

floating node at the comparator’s input. The con-

version algorithm operates on this fixed charge,

and the signal at the analog input pin is ignored.

In effect, the entire DAC capacitor array serves

as analog memory during conversion much like a

hold capacitor in a sample/hold amplifier.

The conversion consists of manipulating the free

plates of the capacitor array to VREF and AGND

to form a capacitive divider. Since the charge at

the floating node remains fixed, the voltage at

that point depends on the proportion of capaci-

tance ti ed to VREF versus AGND. Th e

successive-approximation algorithm is used to

find the proportion of capacitance, which when

connected to the reference will drive the voltage

at the floating node to zero. That binary fraction

of capacitance represents the converter’s digital

output.

AIN

C

C/2

C/32,768

MSB

LSB

Bit 15

Bit 14

Bit 13

Bit 0

C

= C + C/2 + C/4 + C/8 + ... C/32,768

tot

Dummy

C/32,768

S1

C/4

Fine

VREF

AGND

Coarse

Fine

Coarse

Fine

+

-

+

-

+

-

+

-

Figure 1. Coarse Charge Input Buffers and Charge Redistribution DAC

CS5101A CS5102A

12

DS45F2

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9169201MXA | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP28 |

| 5962-9169201Q3C | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC28 |

| 5962-9169201QXC | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP28 |

| 5962-9169301MCA | 4 CHANNEL, VIDEO AMPLIFIER, CDIP14 |

| 5962-9169401MCA | 1 CHANNEL, VIDEO AMPLIFIER, CDIP14 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9169301M2A | 制造商:Texas Instruments 功能描述:-LIFETIME BUYS TIL 03/03 |

| 5962-9169701MMA | 制造商:e2v Aerospace & Defense 功能描述:SMD MKD 87C51RC-16 PHI-JLCC |

| 5962-9169701MUA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intel 功能描述: |

| 5962-9169702MUA | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-9172201MEA | 制造商:e2v 功能描述:Counter Single 4-Bit Binary UP 16-Pin CDIP 制造商:e2v technologies 功能描述:Counter Single 4-Bit Binary UP 16-Pin CDIP |

发布紧急采购,3分钟左右您将得到回复。