- 您现在的位置:买卖IC网 > PDF目录67334 > 5962-9169101M3A (CRYSTAL SEMICONDUCTOR CORP) 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC28 PDF资料下载

参数资料

| 型号: | 5962-9169101M3A |

| 厂商: | CRYSTAL SEMICONDUCTOR CORP |

| 元件分类: | ADC |

| 英文描述: | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC28 |

| 封装: | LCC-28 |

| 文件页数: | 7/48页 |

| 文件大小: | 647K |

| 代理商: | 5962-9169101M3A |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

clock yields a maximum throughput of 20 kHz in

a single channel configuration.

Asynchronous Sampling Considerations

When HOLD goes low, the analog sample is cap-

tured immediately. The HOLD signal is latched

by the next falling edge of CLKIN, and conver-

sion then starts on the subsequent rising edge. If

HOLD is asynchronous to CLKIN, then there

will be a 1.5 CLKIN cycle uncertainty as to when

conversion starts. Considering the CS5101A with an

8 MHz CLKIN, with a 100 kHz HOLD signal, then

this 1.5 CLKIN uncertainty will result in a 1.5

CLKIN period possible reduction in fine charge time

for the next conversion.

This reduced fine charge time will be less than

the minimum specification. If the CLKIN fre-

quency is increased slightly (for example, to

8.192 MHz) then sufficient fine charge time will

always occur. The maximum frequency for

CLKIN is specified at 9.216 MHz; it is recom-

mended that for asynchronous operation at

100 kHz, CLKIN should be between 8.192 MHz

and 9.216 MHz.

Analog Input Range/Coding Format

The reference voltage directly defines the input

voltage range in both the unipolar and bipolar

configurations. In the unipolar configuration

(BP/UP low), the first code transition occurs 0.5

LSB above AGND, and the final code transition

occurs 1.5 LSB’s below VREF. In the bipolar

configuration (BP/UP high), the first code transi-

tion occurs 0.5 LSB above -VREF and the last

transition occurs 1.5 LSB’s below +VREF.

The CS5101A and CS5102A can output data in

either 2’s complement, or binary format. If the

CODE pin is high, the output is in 2’s comple-

ment format with a range of -32,768 to +32,767.

If the CODE pin is low, the output is in binary

format with a range of 0 to +65,535. See Table 1

for output coding.

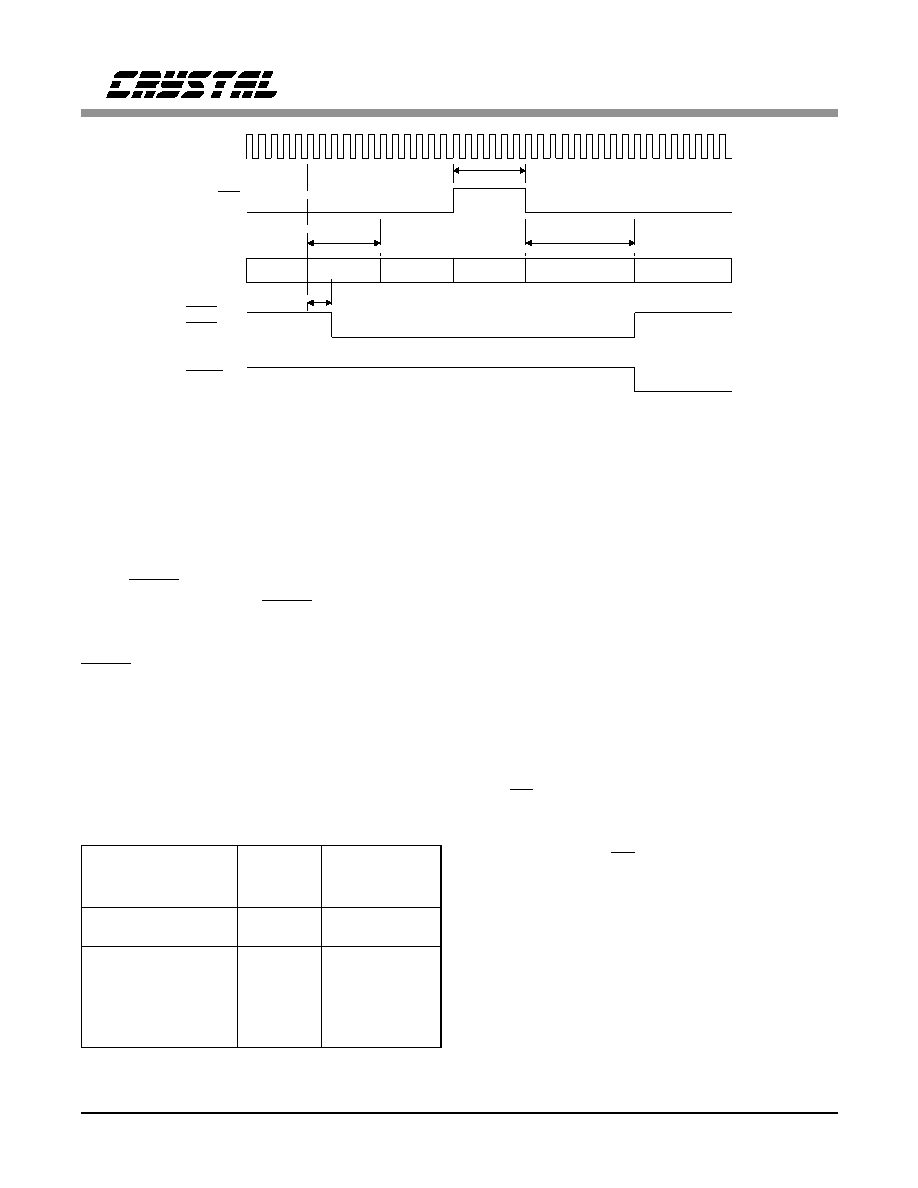

CLKIN

CRS/FIN

Internal

Status

Conv.

Coarse

Fine Chg.

Coarse

Fine Chg.

Conv.

TRK1 or

TRK2

HOLD

Min: 1.125

s*

6 clk

2 clk

Min: 750 ns*

3.75

s**

5.625

s**

* Applies to 5101A

** Applies to 5102A

Figure 2. Coarse-Charge/Fine-Charge Control

Unipolar Input

Voltage

Offset

Binary

Two’s

Complement

Bipolar Input

Voltage

>(VREF-1.5 LSB) FFFF

7FFF

>(VREF-1.5 LSB)

VREF-1.5 LSB

FFFF

FFFE

7FFF

7FFE

VREF-1.5 LSB

VREF/2-0.5 LSB

8000

7FFF

0000

FFFF

-0.5 LSB

+0.5 LSB

0001

0000

8001

8000

-VREF+0.5 LSB

<(+0.5 LSB)

0000

8000

<(-VREF+0.5 LSB)

Table 1. Output Coding

CS5101A CS5102A

DS45F2

15

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9169201MXA | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP28 |

| 5962-9169201Q3C | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CQCC28 |

| 5962-9169201QXC | 2-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, CDIP28 |

| 5962-9169301MCA | 4 CHANNEL, VIDEO AMPLIFIER, CDIP14 |

| 5962-9169401MCA | 1 CHANNEL, VIDEO AMPLIFIER, CDIP14 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9169301M2A | 制造商:Texas Instruments 功能描述:-LIFETIME BUYS TIL 03/03 |

| 5962-9169701MMA | 制造商:e2v Aerospace & Defense 功能描述:SMD MKD 87C51RC-16 PHI-JLCC |

| 5962-9169701MUA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intel 功能描述: |

| 5962-9169702MUA | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-9172201MEA | 制造商:e2v 功能描述:Counter Single 4-Bit Binary UP 16-Pin CDIP 制造商:e2v technologies 功能描述:Counter Single 4-Bit Binary UP 16-Pin CDIP |

发布紧急采购,3分钟左右您将得到回复。