- 您现在的位置:买卖IC网 > PDF目录122717 > 935267488112 (NXP SEMICONDUCTORS) 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | 935267488112 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDSO20 |

| 封装: | 7.50 MM, PLASTIC, SO-20 |

| 文件页数: | 16/69页 |

| 文件大小: | 352K |

| 代理商: | 935267488112 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

Philips Semiconductors

Preliminary specification

87LPC768

Low power, low price, low pin count (20 pin) microcontroller with

4 kB OTP 8-bit A/D, Pulse Width Modulator

2000 May 02

21

BIT

SYMBOL

FUNCTION

I2CON.7

RDAT

Read: the most recently received data bit.

“

CXA

Write: clears the transmit active flag.

I2CON.6

ATN

Read: ATN = 1 if any of the flags DRDY, ARL, STP, or STP = 1.

“

IDLE

Write: in the I2C slave mode, writing a 1 to this bit causes the I2C hardware to ignore the bus until it

is needed again.

I2CON.5

DRDY

Read: Data Ready flag, set when there is a rising edge on SCL.

“

CDR

Write: writing a 1 to this bit clears the DRDY flag.

I2CON.4

ARL

Read: Arbitration Loss flag, set when arbitration is lost while in the transmit mode.

“

CARL

Write: writing a 1 to this bit clears the CARL flag.

I2CON.3

STR

Read: Start flag, set when a start condition is detected at a master or non-idle slave.

“

CSTR

Write: writing a 1 to this bit clears the STR flag.

I2CON.2

STP

Read: Stop flag, set when a stop condition is detected at a master or non-idle slave.

“

CSTP

Write: writing a 1 to this bit clears the STP flag.

I2CON.1

MASTER

Read: indicates whether this device is currently as bus master.

“

XSTR

Write: writing a 1 to this bit causes a repeated start condition to be generated.

I2CON.0

—

Read: undefined.

“

XSTP

Write: writing a 1 to this bit causes a stop condition to be generated.

* Due to the manner in which bit addressing is implemented in the 80C51 family, the I2CON register should never be altered by

use of the SETB, CLR, CPL, MOV (bit), or JBC instructions. This is due to the fact that read and write functions of this register

are different. Testing of I2CON bits via the JB and JNB instructions is supported.

—

SU01155

MASTER

STP

STR

ARL

DRDY

ATN

RDAT

0

1

2

3

4

5

6

7

I2CON

Reset Value: 81h

Bit Addressable*

Address: D8h

XSTP

XSTR

CSTP

CSTR

CARL

CDR

IDLE

CXA

READ

WRITE

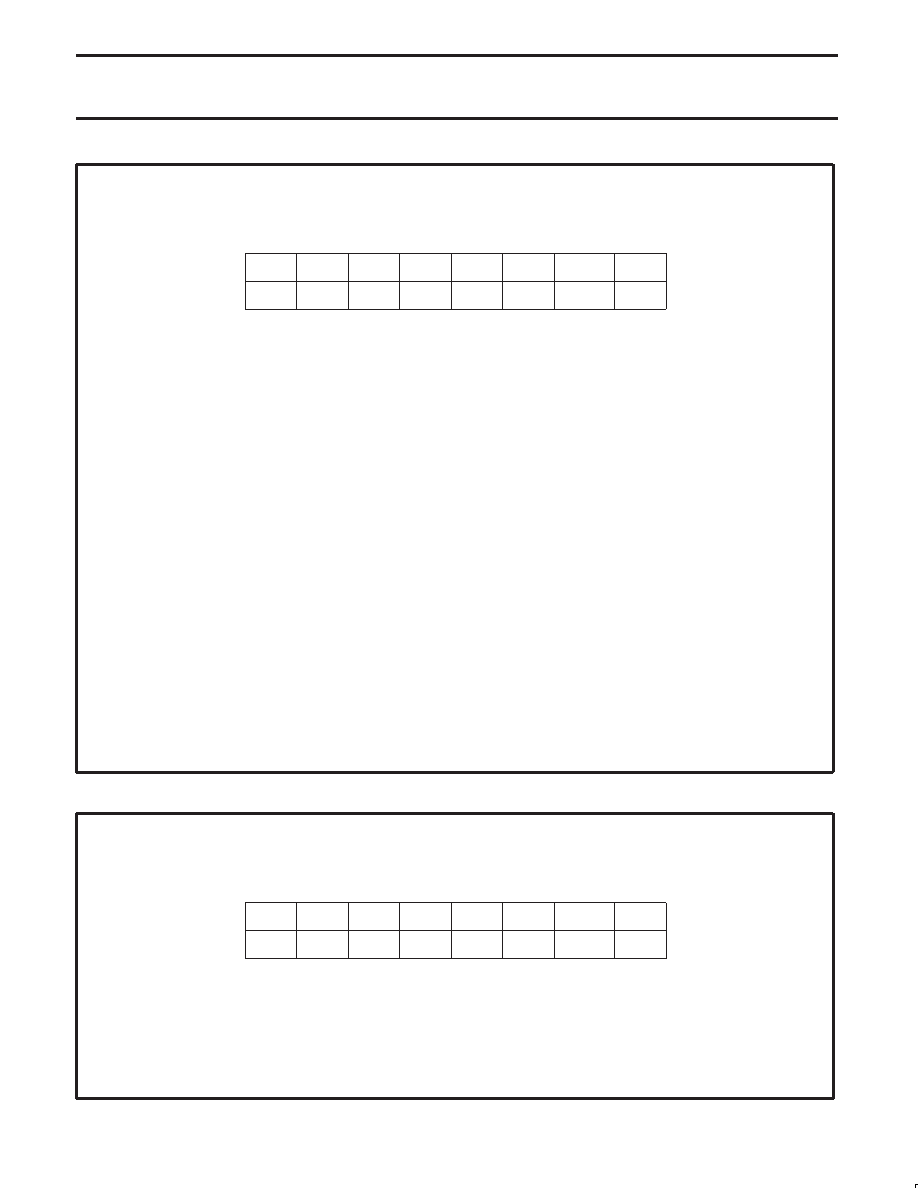

Figure 9. I2C Control Register (I2CON)

BIT

SYMBOL

FUNCTION

I2DAT.7

RDAT

Read: the most recently received data bit, captured from SDA at every rising edge of SCL. Reading

I2DAT also clears DRDY and the Transmit Active state.

“

XDAT

Write: sets the data for the next transmitted bit. Writing I2DAT also clears DRDY and sets the

Transmit Active state.

I2DAT.6–0

–

Unused.

—

SU01156

—

RDAT

0

1

2

3

4

5

6

7

I2DAT

Reset Value: xxh

Not Bit Addressable

Address: D9h

—

XDAT

READ

WRITE

Figure 10. I2C Data Register (I2DAT)

相关PDF资料 |

PDF描述 |

|---|---|

| 9ERS3165BGILF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 9LPRS535BFLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 935208500112 | 8-BIT, 16 MHz, MICROCONTROLLER, PDIP40 |

| 935208540112 | 8-BIT, 16 MHz, MICROCONTROLLER, PQCC44 |

| 935267591518 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

发布紧急采购,3分钟左右您将得到回复。