- 您现在的位置:买卖IC网 > PDF目录166373 > A3P-L67201V-55 (ATMEL WIRELESS MICROCONTROLLERS) 512 X 9 OTHER FIFO, 55 ns, PDIP28 PDF资料下载

参数资料

| 型号: | A3P-L67201V-55 |

| 厂商: | ATMEL WIRELESS MICROCONTROLLERS |

| 元件分类: | FIFO |

| 英文描述: | 512 X 9 OTHER FIFO, 55 ns, PDIP28 |

| 封装: | 0.300 INCH, PLASTIC, DIP-28 |

| 文件页数: | 10/16页 |

| 文件大小: | 146K |

| 代理商: | A3P-L67201V-55 |

L 67201/L 67202

MATRA MHS

Rev. C (10/11/95)

3

Pin Names

NAMES

DESCRIPTION

I0–8

Inputs

Q0–8

Outputs

W

Write Enable

R

Read Enable

RS

Reset

EF

Empty Flag

NAMES

DESCRIPTION

FF

Full Flag

XO/HF

Expansion Out/Half–Full Flag

XI

Expansion IN

FL/RT

First Load/Retransmit

VCC

Power Supply

GND

Ground

Signal Description

Data In (I0 - I8)

Data inputs for 9 - bit data

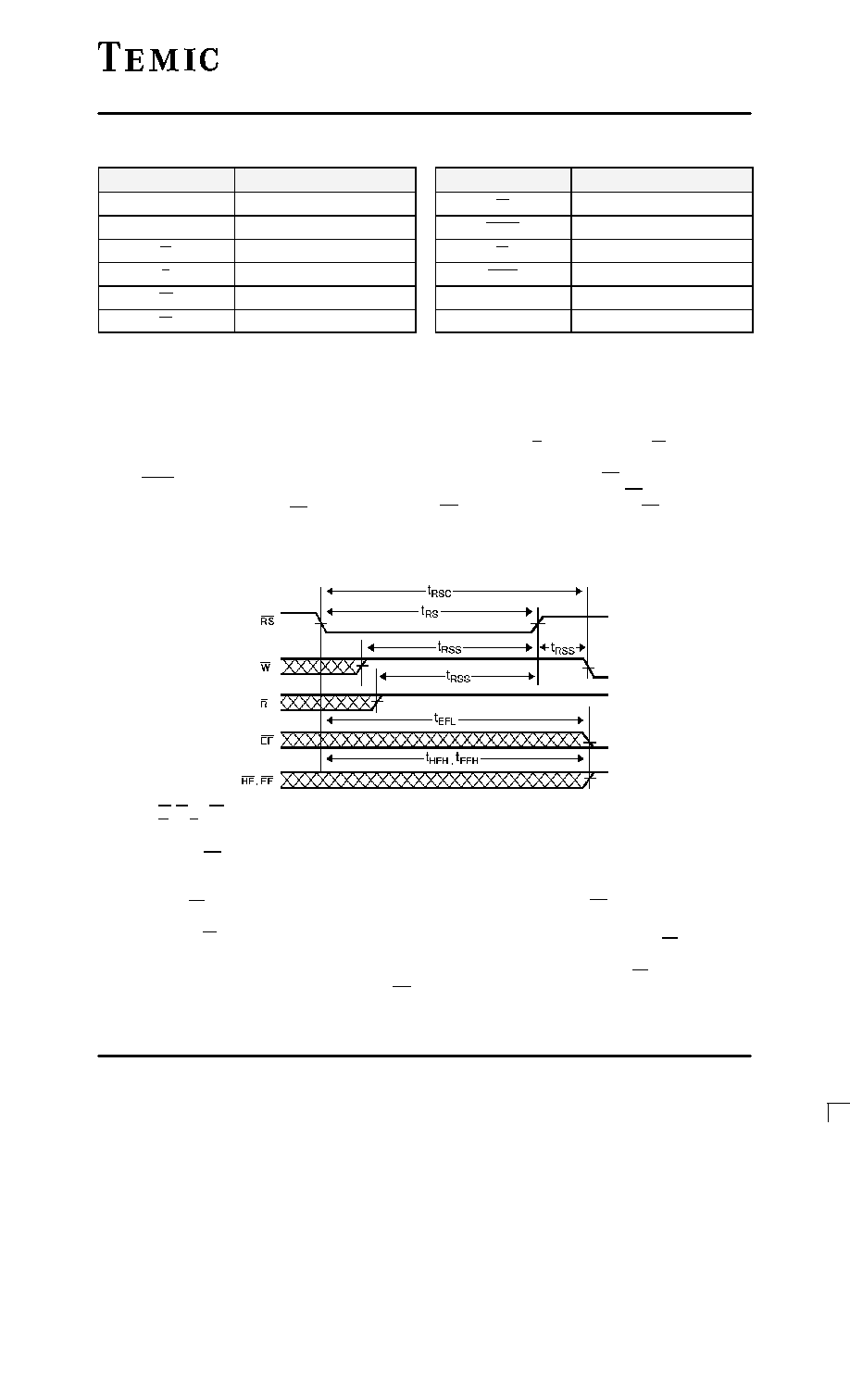

Reset (RS)

Reset occurs whenever the Reset (RS) input is taken to a

low state. Reset returns both internal read and write

pointers to the first location. A reset is required after

power-up before a write operation can be enabled. Both

the Read Enable (R) and Write Enable (W) inputs must be

in the high state during the period shown in figure 1 (i.e.

tRSS before the rising edge of RS) and should not change

until tRSR after the rising edge of RS. The Half-Full flag

(HF will be reset to high after Reset (RS).

Figure 1. Reset.

Notes :

1. EF, FF and HF may change status during reset, but flags will be valid at tRSC.

2. W and R = VIH around the rising edge of RS.

Write Enable (W)

A write cycle is initiated on the falling edge of this input

if the Full Flag (FF) is not set. Data set-up and hold times

must be maintained in the rise time of the leading edge of

the Write Enable (W). Data is stored sequentially in the

Ram array, regardless of any current read operation.

Once half of the memory is filled, and during the falling

edge of the next write operation, the Half-Full Flag (HF)

will be set to low and remain in this state until the

difference between the write and read pointers is less than

or equal to half of the total available memory in the

device. The Half-Full Flag (HF) is then reset by the rising

edge of the read operation.

To prevent data overflow, the Full Flag (FF) will go low,

inhibiting further write operations. On completion of a

valid read operation, the Full Flag (FF) will go high after

TRFF, allowing a valid write to begin. When the FIFO

相关PDF资料 |

PDF描述 |

|---|---|

| A3P-L67202L-65 | 1K X 9 OTHER FIFO, 65 ns, PDIP28 |

| ASI-L67201L-60 | 512 X 9 OTHER FIFO, 60 ns, PQCC32 |

| ATIR0721DS | POSITION, LINEAR SENSOR-DIFFUSE, 1-1mm, 3mA, RECTANGULAR, SURFACE MOUNT |

| ATIR0821DS | POSITION, LINEAR SENSOR-DIFFUSE, 1-1mm, 3mA, RECTANGULAR, THROUGH HOLE MOUNT |

| ATL80/25-256VM | FPGA, 15600 GATES |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PMGB1Y14ASP2 | 制造商:APEM 功能描述:16mm Industrial Control |

| A3PMIS | 制造商:Pentair Technical Products / Hoffman 功能描述:3R Pad Mound Insect Screen , , Steel 制造商:PENTAIR TECNICAL PRODCUTS 功能描述:3R Pad Mound Insect Screen |

| A3PN010-1QNG48 | 功能描述:IC FPGA NANO 10K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN010-1QNG48I | 功能描述:IC FPGA NANO 10K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN010-2QNG48 | 功能描述:IC FPGA NANO 10K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。