- 您现在的位置:买卖IC网 > PDF目录166373 > A3P-L67201V-55 (ATMEL WIRELESS MICROCONTROLLERS) 512 X 9 OTHER FIFO, 55 ns, PDIP28 PDF资料下载

参数资料

| 型号: | A3P-L67201V-55 |

| 厂商: | ATMEL WIRELESS MICROCONTROLLERS |

| 元件分类: | FIFO |

| 英文描述: | 512 X 9 OTHER FIFO, 55 ns, PDIP28 |

| 封装: | 0.300 INCH, PLASTIC, DIP-28 |

| 文件页数: | 13/16页 |

| 文件大小: | 146K |

| 代理商: | A3P-L67201V-55 |

L 67201/L 67202

MATRA MHS

Rev. C (10/11/95)

6

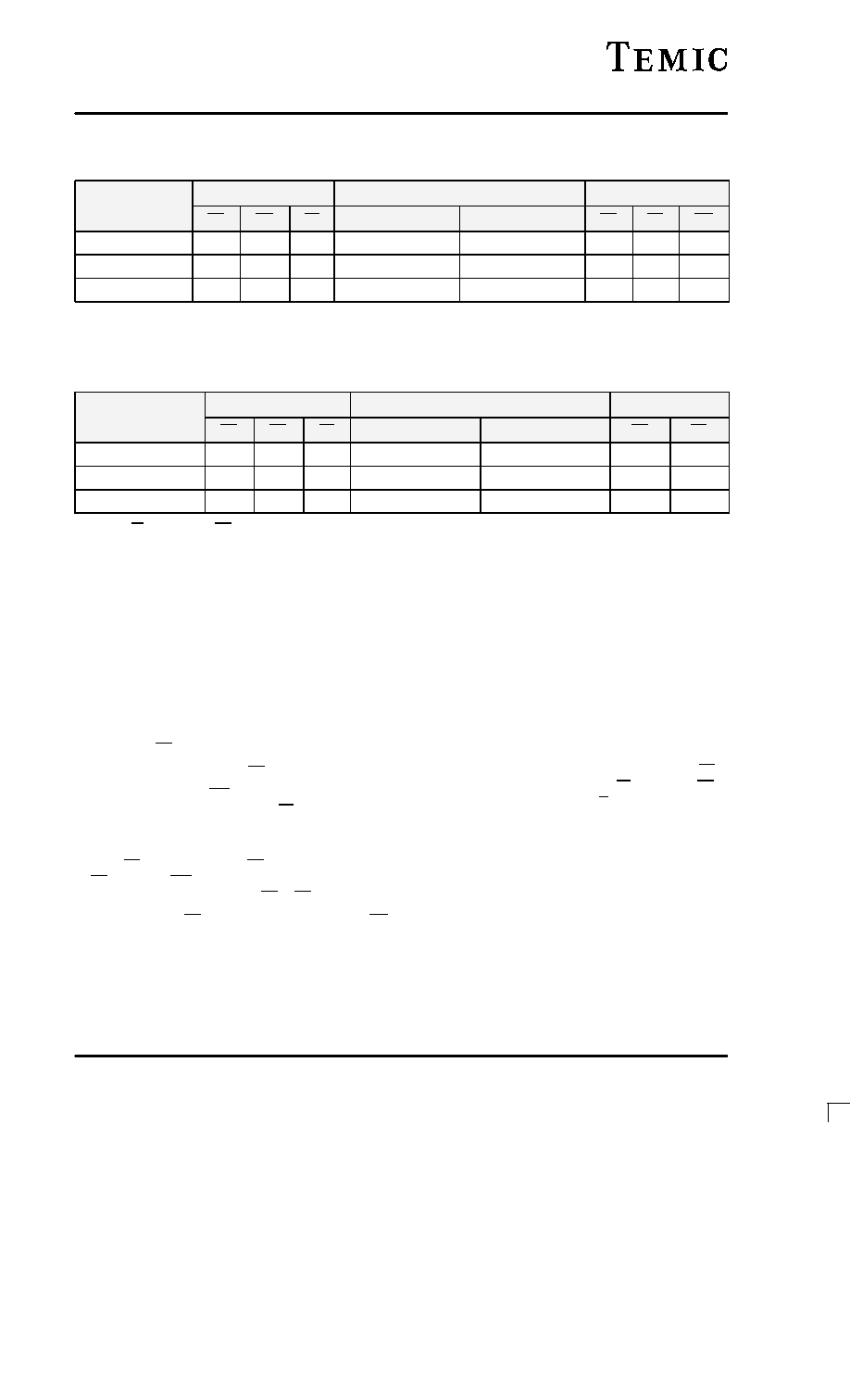

Table 1 : Reset and retransmit

Single Device Configuration/Width Expansion Mode

MODE

INPUTS

INTERNAL STATUS

OUTPUTS

MODE

RS

RT

XI

Read Pointer

Write Pointer

EF

FF

HF

Reset

0

X

0

Location Zero

0

1

Retransmit

1

0

Location Zero

Unchanged

X

Read/Write

1

0

Increment(4)

X

Note :

4. Pointer will increment if flag is high.

Table 2 : Reset and First Load Truth Table

Depth Expansion/Compound Expansion Mode

MODE

INPUTS

INTERNAL STATUS

OUTPUTS

MODE

RS

FL

XI

Read Pointer

Write Pointer

EF

FF

Reset First Device

0

(5)

Location Zero

0

1

Reset All Other Devices

0

1

(5)

Location Zero

0

1

Read/Write

1

X

(5)

X

Note :

5. XI is connected to XO of previous device.

See fig. 5.

Depth Expansion (Daisy Chain) Mode

The L 67201/202 can be easily adapted for applications

which require more than 512/1024 words. Figure 4

demonstrates Depth Expansion using three L 67201/202.

Any depth can be achieved by adding additional

67201/202.

The L 67201/202 operate in the Depth Expansion

configuration if the following conditions are met :

1. The first device must be designated by connecting the

First Load (FL) control input to ground.

2. All other devices must have FL in the high state.

3. The Expansion Out (XO) pin of each device must be

connected to the Expansion In (XI) pin of the next

device. See figure 4.

4. External logic is needed to generate a composite Full

Flag (FF) and Empty Flag (EF). This requires that all

EF’s and all FFs be Red (i.e. all must be set to

generate the correct composite FF or EF). See figure 4.

5. The Retransmit (RT) function and Half-Full Flag (HF)

are not available in the Depth Expansion Mode.

Compound Expansion Module

It is quite simple to apply the two expansion techniques

described above together to create large FIFO arrays (see

figure 5).

Bidirectional Mode

Applications which require data buffering between two

systems (each system being capable of Read and Write

operations) can be created by coupling L 67201/202 as

shown in figure 6. Care must be taken to ensure that the

appropriate flag is monitored by each system (i.e. FF is

monitored on the device on which W is in use ; EF is

monitored on the device on which R is in use). Both Depth

Expansion and Width Expansion may be used in this

mode.

Data Flow - Through Modes

Two types of flow-through modes are permitted : a read

flow-through and a write flow-through mode. In the read

flow-through mode (figure 17) the FIFO stack allows a

相关PDF资料 |

PDF描述 |

|---|---|

| A3P-L67202L-65 | 1K X 9 OTHER FIFO, 65 ns, PDIP28 |

| ASI-L67201L-60 | 512 X 9 OTHER FIFO, 60 ns, PQCC32 |

| ATIR0721DS | POSITION, LINEAR SENSOR-DIFFUSE, 1-1mm, 3mA, RECTANGULAR, SURFACE MOUNT |

| ATIR0821DS | POSITION, LINEAR SENSOR-DIFFUSE, 1-1mm, 3mA, RECTANGULAR, THROUGH HOLE MOUNT |

| ATL80/25-256VM | FPGA, 15600 GATES |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PMGB1Y14ASP2 | 制造商:APEM 功能描述:16mm Industrial Control |

| A3PMIS | 制造商:Pentair Technical Products / Hoffman 功能描述:3R Pad Mound Insect Screen , , Steel 制造商:PENTAIR TECNICAL PRODCUTS 功能描述:3R Pad Mound Insect Screen |

| A3PN010-1QNG48 | 功能描述:IC FPGA NANO 10K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN010-1QNG48I | 功能描述:IC FPGA NANO 10K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN010-2QNG48 | 功能描述:IC FPGA NANO 10K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。