参数资料

| 型号: | A40MX02-2PLG68 |

| 厂商: | Microsemi SoC |

| 文件页数: | 13/142页 |

| 文件大小: | 0K |

| 描述: | IC FPGA MX SGL CHIP 3K 68-PLCC |

| 标准包装: | 19 |

| 系列: | MX |

| 输入/输出数: | 57 |

| 门数: | 3000 |

| 电源电压: | 3 V ~ 3.6 V,4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 68-LCC(J 形引线) |

| 供应商设备封装: | 68-PLCC(24.23x24.23) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页

40MX and 42MX FPGA Families

Re vi s i on 11

1-7

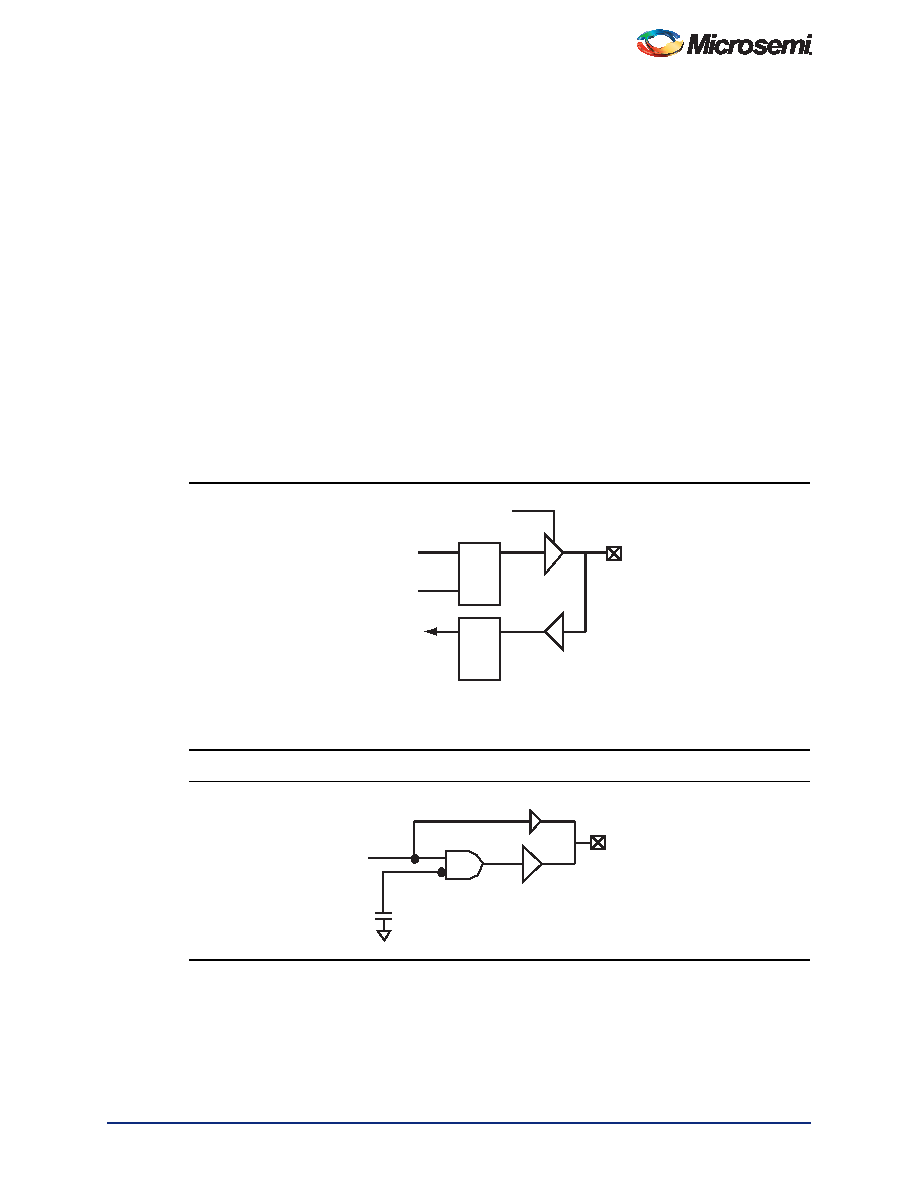

MultiPlex I/O Modules

42MX devices feature Multiplex I/Os and support 5.0V, 3.3V, and mixed 3.3V/5.0V operations.

The MultiPlex I/O modules provide the interface between the device pins and the logic array. Figure 1-9

is a block diagram of the 42MX I/O module. A variety of user functions, determined by a library macro

selection, can be implemented in the module. (Refer to the Antifuse Macro Library Guide for more

information.) All 42MX I/O modules contain tristate buffers, with input and output latches that can be

configured for input, output, or bidirectional operation.

All 42MX devices contain flexible I/O structures, where each output pin has a dedicated output-enable

control (Figure 1-9). The I/O module can be used to latch input or output data, or both, providing fast set-

up time. In addition, the Designer software tools can build a D-type flip-flop using a C-module combined

with an I/O module to register input and output signals. Refer to the Antifuse Macro Library Guide for

more details.

A42MX24 and A42MX36 devices also offer selectable PCI output drives, enabling 100% compliance with

version 2.1 of the PCI specification. For low-power systems, all inputs and outputs are turned off to

reduce current consumption to below 500

μA.

To achieve 5.0V or 3.3V PCI-compliant output drives on A42MX24 and A42MX36 devices, a chip-wide

PCI fuse is programmed via the Device Selection Wizard in the Designer software (Figure 1-10). When

the PCI fuse is not programmed, the output drive is standard.

Designer software development tools provide a design library of I/O macro functions that can implement

all I/O configurations supported by the MX FPGAs.

Note:

*Can be configured as a Latch or D Flip-Flop (Using

C-Module)

Figure 1-9

42MX I/O Module

Figure 1-10 PCI Output Structure of A42MX24 and A42MX36 Devices

Q

D

From Array

To Array

G/CLK*

Q

D

PAD

EN

Signal

PCI Enable

PCI

Fuse

Drive

STD

Output

相关PDF资料 |

PDF描述 |

|---|---|

| RMA49DRSI-S288 | CONN EDGECARD 98POS .125 EXTEND |

| RSM44DRYN | CONN EDGECARD 88POS DIP .156 SLD |

| RMM44DRYN | CONN EDGECARD 88POS DIP .156 SLD |

| RSM43DRYI | CONN EDGECARD 86POS DIP .156 SLD |

| RMM43DRYI | CONN EDGECARD 86POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A40MX02-2PLG68I | 功能描述:IC FPGA MX SGL CHIP 3K 68-PLCC RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:90 系列:ProASIC3 LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:36864 输入/输出数:157 门数:250000 电源电压:1.425 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 125°C 封装/外壳:256-LBGA 供应商设备封装:256-FPBGA(17x17) |

| A40MX02-2PQ100 | 功能描述:IC FPGA MX SGL CHIP 3K 100-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:90 系列:ProASIC3 LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:36864 输入/输出数:157 门数:250000 电源电压:1.425 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 125°C 封装/外壳:256-LBGA 供应商设备封装:256-FPBGA(17x17) |

| A40MX02-2PQ100I | 功能描述:IC FPGA MX SGL CHIP 3K 100-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:90 系列:ProASIC3 LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:36864 输入/输出数:157 门数:250000 电源电压:1.425 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 125°C 封装/外壳:256-LBGA 供应商设备封装:256-FPBGA(17x17) |

| A40MX02-2PQ100M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| A40MX02-2PQG100 | 功能描述:IC FPGA MX SGL CHIP 3K 100-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:90 系列:ProASIC3 LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:36864 输入/输出数:157 门数:250000 电源电压:1.425 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 125°C 封装/外壳:256-LBGA 供应商设备封装:256-FPBGA(17x17) |

发布紧急采购,3分钟左右您将得到回复。