- 您现在的位置:买卖IC网 > PDF目录364584 > A63L73321SERIES 128K X 32 Bit Synchronous High Speed SRAM with Burst Counter and Flow-through Data Output PDF资料下载

参数资料

| 型号: | A63L73321SERIES |

| 元件分类: | 通用总线功能 |

| 英文描述: | 128K X 32 Bit Synchronous High Speed SRAM with Burst Counter and Flow-through Data Output |

| 中文描述: | 128K的× 32位同步计数器高的Burst SRAM的速度和流量,通过数据输出 |

| 文件页数: | 14/17页 |

| 文件大小: | 270K |

| 代理商: | A63L73321SERIES |

A63L73321 Series

PRELIMINARY (June, 1999, Version 0.1)

13

AMIC Technology, Inc.

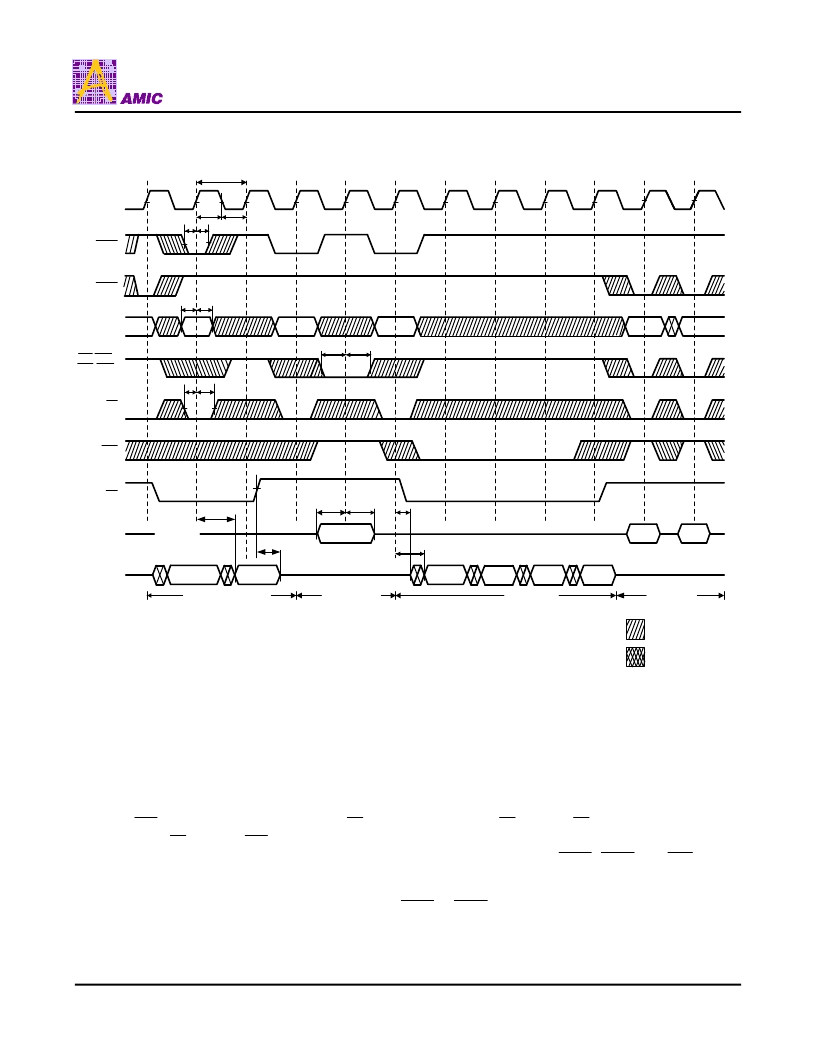

Timing Waveforms (continued)

Read/Write Timing

Notes: 1. Q(A4) refers to output from address A4. Q(A4+1) refers to output from the next internal burst address following

A4.

2.

CE2

and CE2 have timing identical to

CE

. On this diagram, when

CE

is LOW,

CE

is LOW and CE2 is HIGH,

When

CE

is HIGH,

CE2

is HIGH and CE2 is LOW.

3. The data bus (Q) remains in High-Z following a WRITE cycle unless an

ADSP

,

ADSC

, or

ADV

cycle is

performed.

4. Byte Write enables are decided by means of a Write truth table.

5. Back-to-back READs may be controlled by either

ADSP

or

ADSC

CLK

ADSP

ADSC

ADDRESS

A1

A3

CE

(NOTE 2)

ADV

OE

D(A3)

D(A5)

D(A6)

High-Z

DIN

t

CEH

t

CES

t

ADSH

t

ADSS

t

KL

t

KH

t

KC

A2

A4

A5

A6

GW,BWE,

BW1-BW4

(NOTE 3)

Q(A1)

Q(A2)

Q(A4)

Q(A4+1)

DOUT

Back-to-Back READs

Single WRITE

BURST READ

Back-to-Back

WRITEs

(NOTE 1)

t

KQ

t

OELZ

t

DH

t

DS

t

WS

t

WH

t

AS

t

AH

Q(A4+2)

Q(A4+3)

t

OEHZ

t

KQ

Don't Care

Undefined

相关PDF资料 |

PDF描述 |

|---|---|

| A6402 | Telecomm/Datacomm |

| a6402 | Universal Asynchronous Receiver/Transmitter(通用异步接收/传送器) |

| A65-1 | Analog IC |

| A655NV400C5 | Interface IC |

| 697NV400C5 | Microprocessor Supervisory Circuits |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A63L7332E-42 | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:128K X 32 Bit Synchronous High Speed SRAM with Burst Counter and Pipelined Data Output |

| A63L7332E-45 | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:128K X 32 Bit Synchronous High Speed SRAM with Burst Counter and Pipelined Data Output |

| A63L7332E-5 | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:128K X 32 Bit Synchronous High Speed SRAM with Burst Counter and Pipelined Data Output |

| A63L7332SERIES | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:128K X 32 Bit Synchronous High Speed SRAM with Burst Counter and Pipelined Data Output |

| A63L7336 | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:128K X 36 Bit Synchronous High Speed SRAM with Burst Counter and Pipelined Data Output |

发布紧急采购,3分钟左右您将得到回复。