- 您现在的位置:买卖IC网 > PDF目录298813 > ACT-7000ASC-225F24Q 64-BIT, 225 MHz, RISC PROCESSOR, CQFP208 PDF资料下载

参数资料

| 型号: | ACT-7000ASC-225F24Q |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, 225 MHz, RISC PROCESSOR, CQFP208 |

| 封装: | 1.120 X 1.120 INCH, INVERTED, CERAMIC, QFP-208 |

| 文件页数: | 15/26页 |

| 文件大小: | 231K |

| 代理商: | ACT-7000ASC-225F24Q |

22

SCD7000A Rev C 9/9/09

Aeroflex Plainview

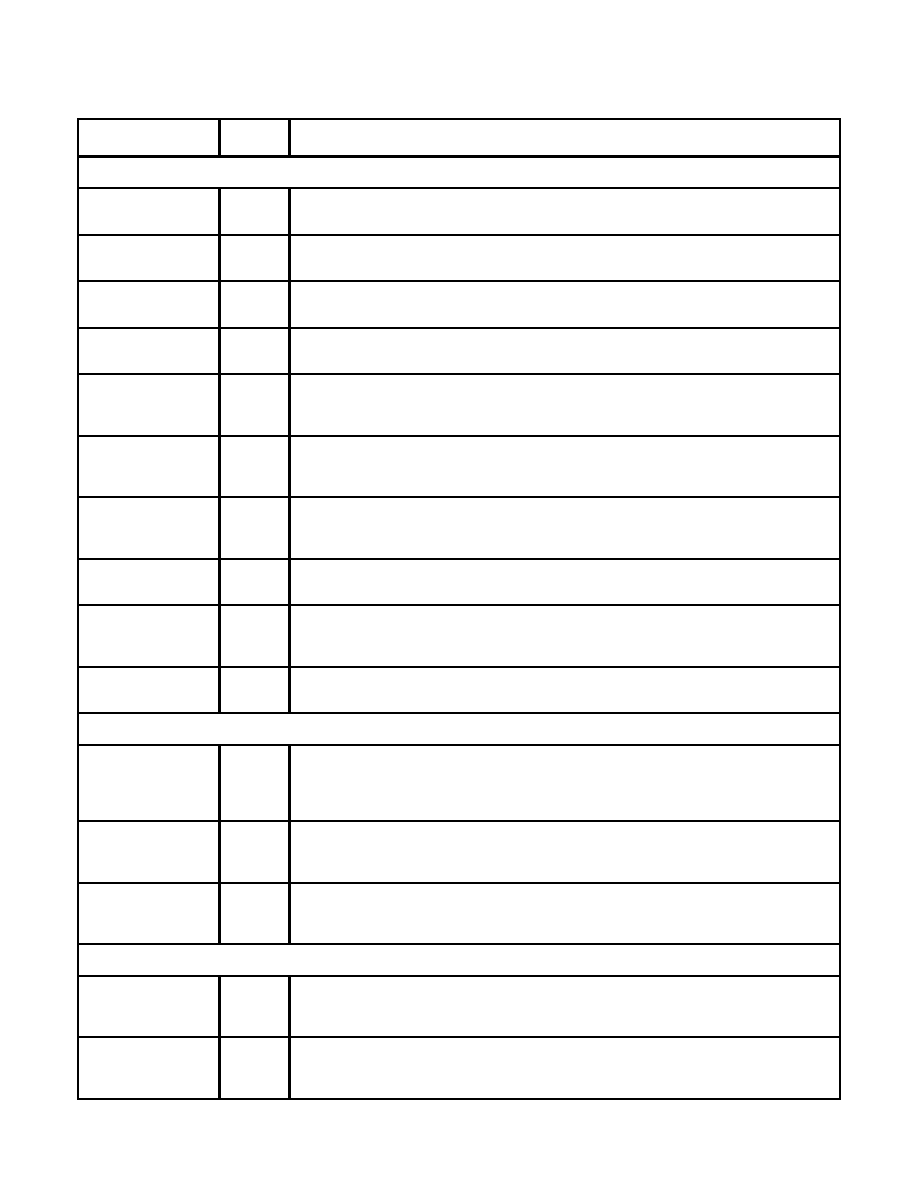

Pin Descriptions

The following is a list of control, data, clock, interrupt, and miscellaneous pins of the ACT 7000ASC.

Pin Name

Type

Description

System interface:

ExtRqst*

Input

External request

Signals that the system interface is submitting an external request.

Release*

Output

Release interface

Signals that the processor is releasing the system interface to slave state

RdRdy*

Input

Read Ready

Signals that an external agent can now accept a processor read.

WrRdy*

Input

Write Ready

Signals that an external agent can now accept a processor write request.

ValidIn*

Input

Valid Input

Signals that an external agent is now driving a valid address or data on the

SysAD bus and a valid command or data identifier on the SysCmd bus.

ValidOut*

Output

Valid output

Signals that the processor is now driving a valid address or data on the SysAD

bus and a valid command or data identifier on the SysCmd bus.

SysAD(63:0)

Input/

Output

System address/data bus

A 64-bit address and data bus for communication between the processor and an

external agent.

SysADC(7:0)

Input/

Output

System address/data check bus

An 8-bit bus containing parity check bits for the SysAD bus during data cycles.

SysCmd(8:0)

Input/

Output

System command/data identifier bus

A 9-bit bus for command and data identifier transmission between the processor

and an external agent.

SysCmdP

Input/

Output

System Command/Data Identifier Bus Parity

For the RM7000A, unused on input and zero on output.

Clock/Control interface:

SysClock

Input

System clock

Master clock input used as the system interface reference clock. All output

timings are relative to this input clock. Pipeline operation frequency is derived by

multiplying this clock up by the factor selected during boot initialization

VccP

Input

Vcc for PLL

Quiet VccInt for the internal phase locked loop. Must be connected to VccInt.

See Figure 10 for additional PPL filtering information.

VssP

Input

Vss for PLL

Quiet Vss for the internal phase locked loop. Must be connected to Vss.

See Figure 10 for additional PPL filtering information.

Interrupt Interface

Int*(5:0)

Input

Interrupt

Six general processor interrupts, bit-wise ORed with bits 5:0 of the interrupt

register.

NMI*

Input

Non-maskable interrupt

Non-maskable interrupt, ORed with bit 15 of the interrupt register (bit 6 in R5000

compatibility mode).

相关PDF资料 |

PDF描述 |

|---|---|

| ACT-7000ASC-300F17I | 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 |

| ACT4445 | DATACOM, MIL-STD-1553 DATA BUS TRANSCEIVER, BCC64 |

| ACTS04KMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDFP14 |

| ACTS04DMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDIP14 |

| ACTS08DMSR | ACT SERIES, QUAD 2-INPUT AND GATE, CDIP14 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ACT7000SC | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17C | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17I | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17M | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17Q | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

发布紧急采购,3分钟左右您将得到回复。