参数资料

| 型号: | AD5590BBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/44页 |

| 文件大小: | 0K |

| 描述: | IC ADC I/O PORT16 W/AMP 80CSPBGA |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 1M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 12.5mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LFBGA,CSPBGA |

| 供应商设备封装: | 80-CSP-BGA(10x10) |

| 包装: | 托盘 |

| 输入数目和类型: | 16 个单端,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD5590

Rev. A | Page 33 of 44

LDAC Function

The outputs of all DACs can be updated simultaneously using

the hardware LDAC pin.

Synchronous LDAC: After new data is read, the DAC registers

are updated on the falling edge of the 32nd DSCLK pulse. LDAC

can be permanently low or pulsed as in Figure 4.

Asynchronous LDAC: The outputs are not updated at the same

time that the input registers are written to. When LDAC goes

low, the DAC registers are updated with the contents of the

input register.

Alternatively, the outputs of all DACs can be updated simulta-

neously using the software LDAC function by writing to Input

Register n and updating all DAC registers. Command 0011 is

reserved for this software LDAC function.

An LDAC register gives the user extra flexibility and control

over the hardware LDAC pin. This register allows the user to

select which combination of channels to simultaneously update

when the hardware LDAC pin is executed. Setting the LDAC bit

register to 0 for a DAC channel means that this channel’s update

is controlled by the LDAC pin. If this bit is set to 1, this channel

updates synchronously; that is, the DAC register is updated

after new data is read, regardless of the state of the LDAC pin.

It effectively registers the LDAC pin as being tied low. (See

Table 19 for the LDAC register mode of operation.) This

flexibility is useful in applications where the user wants to

simultaneously update select channels while the rest of the

channels are synchronously updating.

Writing to the DAC using Command 0110 loads the 8-bit

LDAC register (DB7 to DB0). The default for each channel is

0, that is, the LDAC pin works normally. Setting the bits to 1

means the DAC channel is updated regardless of the state of

the LDAC pin. See Table 20 for the contents of the input shift

register during the LDAC register mode of operation.

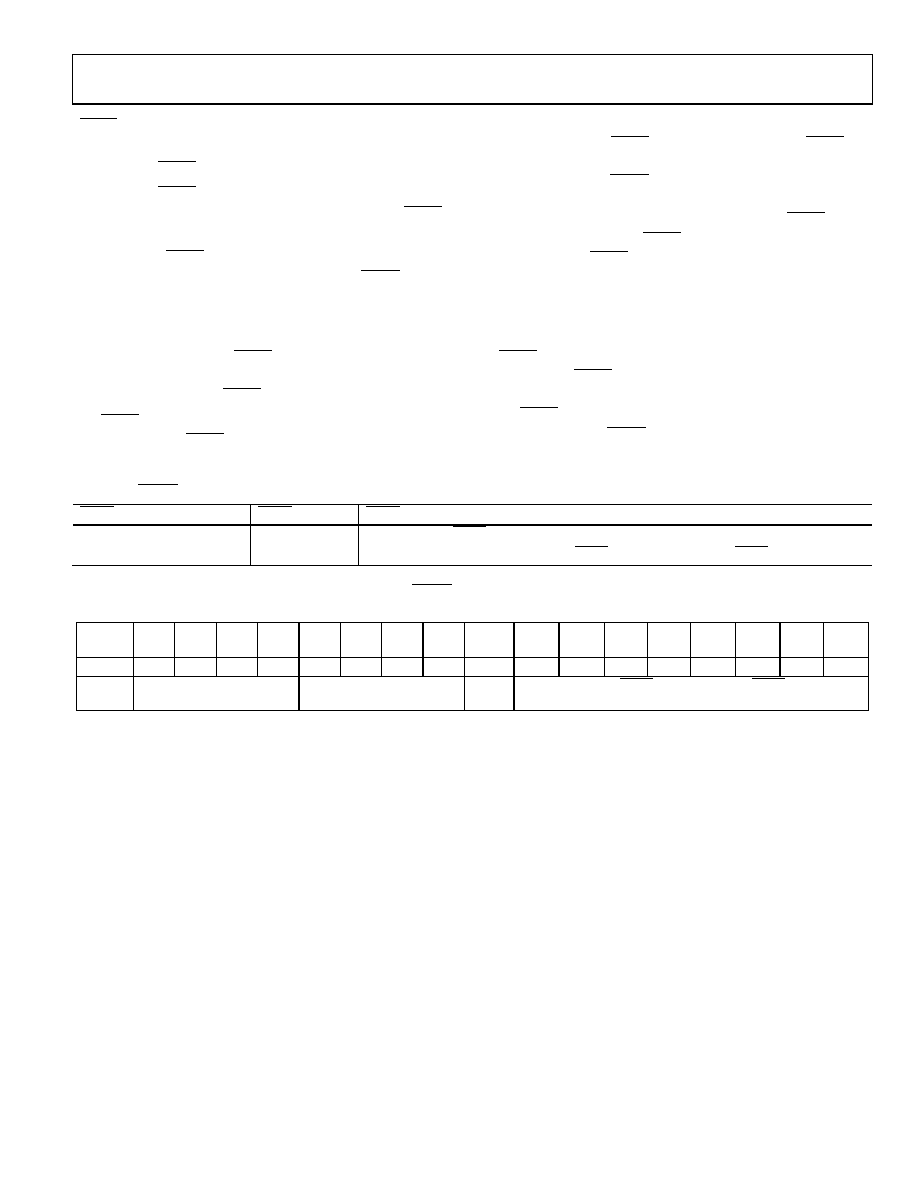

Table 19. LDAC Register

LDAC Bits (DB7 to DB0)

LDAC Pin

LDAC Operation

0

1/0

Determined by LDAC pin.

1

X—don’t care

DAC channels update, overriding the LDAC pin. DAC channels see LDAC as 0.

Table 20. DAC 32-Bit Input Shift Register Contents for LDAC Register Function

MSB

LSB

DB31

to DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20

DB19

to DB8 DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

X

0

1

0

X

DAC H DAC G DAC F DAC E DAC D DAC C DAC B DAC A

Don’t

care

Command bits (C3 to C0)

Address bits (A3 to A0)—

don’t care

Don’t

care

Setting LDAC bit to 1 overrides LDAC pin

相关PDF资料 |

PDF描述 |

|---|---|

| AD5621BKSZ-500RL7 | IC DAC 12BIT SPI 5V SC70-6 |

| AD5626BRMZ-REEL7 | IC DAC NANO 12BIT 8-MSOP |

| AD5662BRM-1 | IC DAC 16BIT BUFF V-OUT 8-MSOP |

| AD5663RBCPZ-3R2 | IC DAC NANO 16BIT DUAL 10-LFCSP |

| AD5664BCPZ-R2 | IC DAC NANO 16BIT QUAD 10-LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5590BBCZ | 功能描述:IC ADC I/O PORT-16 AMP 80-CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD5592RBCBZ-1-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16WLCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:ADC,DAC 分辨率(位):12 b 采样率(每秒):400k 数据接口:SPI 电压源:单电源 电压 - 电源:2.7 V ~ 5.5 V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:16-UFBGA,WLCSP 供应商器件封装:16-WLCSP(1.96x1.96) 标准包装:1 |

| AD5592RBCBZ-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16WLCSP 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD5592RBCPZ-1-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16LFCSP 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD5592RBCPZ-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:ADC,DAC 分辨率(位):12 b 采样率(每秒):400k 数据接口:SPI 电压源:单电源 电压 - 电源:2.7 V ~ 5.5 V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:16-WFQFN,CSP 供应商器件封装:16-LFCSP-WQ(3x3) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。