参数资料

| 型号: | AD5590BBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/44页 |

| 文件大小: | 0K |

| 描述: | IC ADC I/O PORT16 W/AMP 80CSPBGA |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 1M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 12.5mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LFBGA,CSPBGA |

| 供应商设备封装: | 80-CSP-BGA(10x10) |

| 包装: | 托盘 |

| 输入数目和类型: | 16 个单端,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD5590

Rev. A | Page 34 of 44

ACCESSING THE ADC BLOCK

The ADC register can be accessed via the serial interface using

the ASCLK , ADIN, ADOUT, and ASYNC pins. The VDRIVE pin

can be used to dictate the logic levels of the output pins, allow-

ing the ADC to be interfaced to a 3 V DSP while the ADC is

operating at 5 V.

ADC Modes of Operation

The ADC has a number of different modes of operation. These

modes are designed to provide flexible power management options.

These options can be chosen to optimize the power dissipation/

throughput rate ratio for differing application requirements.

The mode of operation of the ADC is controlled by the power

management bits, PM1 and PM0, in the ADC control register,

as detailed in Table 21. When power supplies are first applied to

the ADC, ensure that the ADC is placed in the required mode

of operation (see the Powering Up the ADC section).

Normal Mode (PM1 = PM0 = 1)

This mode is intended for the fastest throughput rate perfor-

mance because the user does not have to worry about any

power-up times with the ADC remaining fully powered at all

times. Figure 64 shows the general diagram of the operation of

the ADC in this mode.

NOTES

1. CONTROL REGISTER DATA IS LOADED ON FIRST 12 SCLK CYCLES.

2. SHADOW REGISTER DATA IS LOADED ON FIRST 16 SCLK CYCLES.

ASYNC

ASCLK

1

16

12

CHANNE L IDENTIFIER BITS + CONVERSION RESULT

DATA IN TO CONTROL/SHADOW REGISTER

ADOUT

ADIN

07691-

064

Figure 64. ADC Normal Mode Operation

The conversion is initiated on the falling edge of ASYNC and

the track-and-hold enters hold mode as described in the Serial

Interface section. The data presented to the ADC on the ADIN

line during the first 12 clock cycles of the data transfer is loaded

to the ADC control register (provided the write bit is 1). If the

previous write had SEQ = 0 and shadow = 1, the data presented on

the ADIN line on the next 16 ASCLK cycles is loaded into the

shadow register. The ADC remains fully powered up in normal

mode at the end of the conversion as long as PM1 and PM0 are

set to 1 in the write transfer during that conversion. To ensure

continued operation in normal mode, PM1 and PM0 are both

loaded with 1 on every data transfer. Sixteen serial clock cycles

are required to complete the conversion and access the conver-

sion result. The track-and-hold returns to track on the 14th

ASCLK falling edge. ASYNC can then idle high until the next

conversion or can idle low until sometime prior to the next

conversion, (effectively idling ASYNC low).

When a data transfer is complete (ADOUT has returned to

three-state, weak/TRI bit = 0), another conversion can be

initiated by bringing ASYNC low again after the quiet time,

tQUIET, has elapsed.

Full Shutdown (PM1 = 1, PM0 = 0)

In this mode, all internal circuitry on the ADC is powered

down. The ADC retains information in the ADC control

register during full shutdown. The ADC remains in full

shutdown until the power management bits in the control

register, PM1 and PM0, are changed.

If a write to the ADC control register occurs while the ADC is

in full shutdown, with the power management bits changed to

PM0 = PM1 = 1, normal mode, the ADC begins to power up

on the ASYNC rising edge. The track-and-hold that was in hold

while the ADC was in full shutdown return to track on the 14th

ASCLK falling edge.

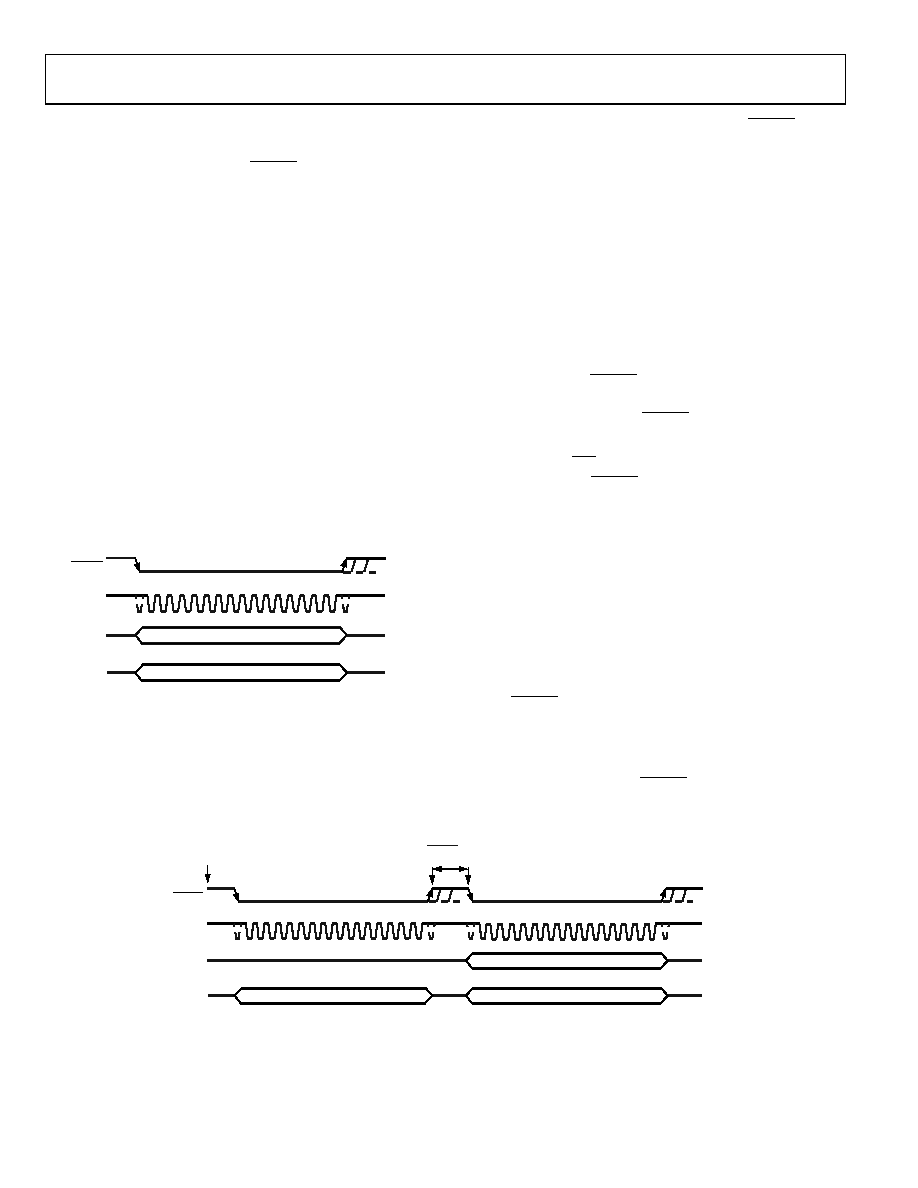

To ensure that the ADC is fully powered up, tPOWER-UP (t12)

should elapse before the next ASYNC falling edge. Figure 65

shows the general diagram for this sequence.

ASCLK

1

16

1

14

16

14

ADOUT

PART IS IN FULL

SHUTDOWN

PART BEGINS TO POWER UP ON ASYNC

RISING EDGE AS PM1 = 1, PM0 = 1

PART IS FULLY POWERED UP

ONCE TPOWER UP HAS ELAPSED

ADIN

ASYNC

t12

CHANNE L IDENTIFIER BITS + CONVERSION RESULT

DATA IN TO CONTROL REGISTER

CONTROL REGISTER IS LOADED ON THE

FIRST 12 CLOCKS, PM1 = 1, PM0 = 1

TO KEEP PART IN NORMAL MODE, LOAD

PM1 = 1, PM0 = 1 IN CONTROL REGISTER

DATA IN TO CONTROL/SHADOW REGISTER

07691-

065

Figure 65. Full Shutdown Mode Operation

相关PDF资料 |

PDF描述 |

|---|---|

| AD5621BKSZ-500RL7 | IC DAC 12BIT SPI 5V SC70-6 |

| AD5626BRMZ-REEL7 | IC DAC NANO 12BIT 8-MSOP |

| AD5662BRM-1 | IC DAC 16BIT BUFF V-OUT 8-MSOP |

| AD5663RBCPZ-3R2 | IC DAC NANO 16BIT DUAL 10-LFCSP |

| AD5664BCPZ-R2 | IC DAC NANO 16BIT QUAD 10-LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5590BBCZ | 功能描述:IC ADC I/O PORT-16 AMP 80-CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD5592RBCBZ-1-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16WLCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:ADC,DAC 分辨率(位):12 b 采样率(每秒):400k 数据接口:SPI 电压源:单电源 电压 - 电源:2.7 V ~ 5.5 V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:16-UFBGA,WLCSP 供应商器件封装:16-WLCSP(1.96x1.96) 标准包装:1 |

| AD5592RBCBZ-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16WLCSP 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD5592RBCPZ-1-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16LFCSP 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD5592RBCPZ-RL7 | 功能描述:IC DAC/ADC 12BIT OCT SPI 16LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:ADC,DAC 分辨率(位):12 b 采样率(每秒):400k 数据接口:SPI 电压源:单电源 电压 - 电源:2.7 V ~ 5.5 V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:16-WFQFN,CSP 供应商器件封装:16-LFCSP-WQ(3x3) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。