- 您现在的位置:买卖IC网 > PDF目录8562 > AD5764CSUZ-REEL7 (Analog Devices Inc)IC DAC 16BIT QUAD BIPO 32-TQFP PDF资料下载

参数资料

| 型号: | AD5764CSUZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/28页 |

| 文件大小: | 0K |

| 描述: | IC DAC 16BIT QUAD BIPO 32-TQFP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 产品变化通告: | AD5764(R), AD5744R Product Change 04/Sept/2009 |

| 设计资源: | High Accuracy, Bipolar Voltage Output Digital-to-Analog Conversion Using AD5764 (CN0006) |

| 标准包装: | 500 |

| 设置时间: | 8µs |

| 位数: | 16 |

| 数据接口: | 串行 |

| 转换器数目: | 4 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 275 mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 4 电压,双极 |

| 采样率(每秒): | 1.26M |

| 配用: | EVAL-AD5764EBZ-ND - BOARD EVAL FOR AD5764 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD5764

Data Sheet

Rev. F | Page 20 of 28

The output voltage expression for the AD5764 is given by

TRANSFER FUNCTION

×

+

×

=

536

,

65

4

2

D

V

REFIN

OUT

relationship for the AD5764 for both offset binary and twos

complement data coding, respectively.

where:

D is the decimal equivalent of the code loaded to the DAC.

VREFIN is the reference voltage applied at the REFAB/REFCD pins.

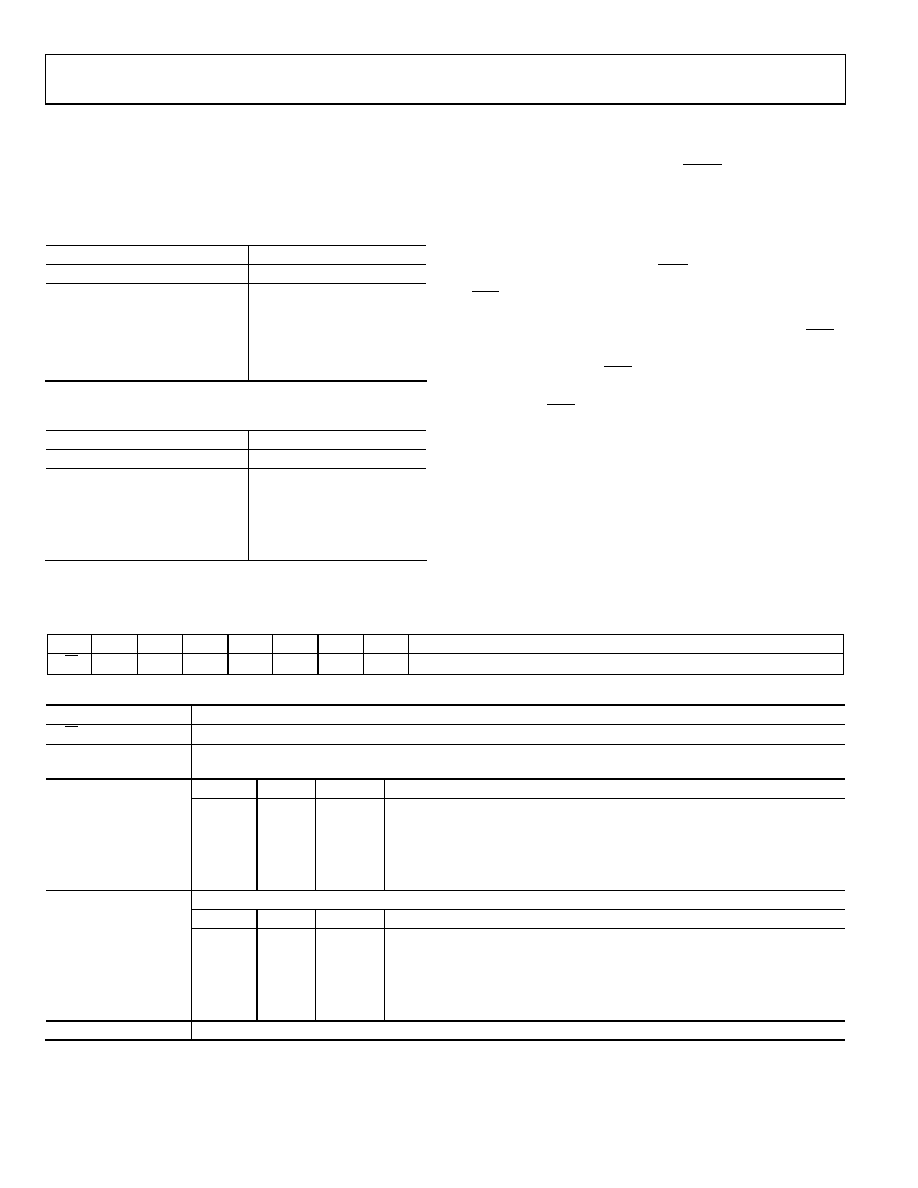

Table 7. Ideal Output Voltage to Input Code Relationship—

Offset Binary Data Coding

Digital Input

Analog Output

ASYNCHRONOUS CLEAR (CLR)

MSB

LSB

VOUTx

1111

+2 VREF × (32,767/32,768)

CLR is a negative edge triggered clear that allows the outputs to

be cleared to either 0 V (twos complement coding) or negative

full scale (offset binary coding). It is necessary to maintain CLR

low for a minimum amount of time (see

) for the operation

to complete. When the

CLR signal is returned high, the output

remains at the cleared value until a new value is programmed. If

at power-on, CLR is at 0 V, then all DAC outputs are updated

with the clear value. A clear can also be initiated through software

by writing Command 0x04XXXX to the AD5764.

1000

0000

0001

+2 VREF × (1/32,768)

1000

0000

0 V

0111

1111

2 VREF × (1/32,768)

0000

2 VREF × (32,767/32,768)

Table 8. Ideal Output Voltage to Input Code Relationship—

Twos Complement Data Coding

Digital Input

Analog Output

MSB

LSB

VOUTx

0111

1111

+2 VREF × (32,767/32,768)

0000

0001

+2 VREF × (1/32,768)

0000

0 V

1111

2 VREF × (1/32,768)

1000

0000

2 VREF × (32,767/32,768)

Table 9. Input Shift Register Bit Map

MSB

LSB

DB23

DB22

DB21

DB20

DB19

DB18

DB17

DB16

DB15:DB0

R/W

0

REG2

REG1

REG0

A2

A1

A0

Data

Table 10. Input Shift Register Bit Functions

Bit

Description

R/W

Indicates a read from or a write to the addressed register.

REG2, REG1, REG0

Used in association with the address bits to determine if a read or write operation is to the data register, offset

register, coarse gain register, fine gain register, or function register.

REG2

REG1

REG0

Function

0

Function register

0

1

0

Data register

0

1

Coarse gain register

1

0

Fine gain register

1

0

1

Offset register

A2, A1, A0

These bits are used to decode the DAC channels.

A2

A1

A0

Channel Address

0

DAC A

0

1

DAC B

0

1

0

DAC C

0

1

DAC D

1

0

All DACs

Data

Data bits.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7834BRZ-REEL | IC DAC 14BIT QUAD SERIAL 28SOIC |

| MAX9654AUB+ | IC AMP FILTER W/SHUTDOWN 10-UMAX |

| DAC8420FS-REEL | IC DAC 12BIT QUAD SRL LP 16-SOIC |

| VI-BNV-MU-S | CONVERTER MOD DC/DC 5.8V 200W |

| LTC2704CGW-14#PBF | IC DAC 14BIT QUAD VOUT 44-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5764R | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete Quad, 16-Bit, High Accuracy, Serial Input, Bipolar Voltage Output DAC |

| AD5764R_08 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete Quad, 16-Bit, High Accuracy, Serial Input, Bipolar Voltage Output DAC |

| AD5764RASUZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete Quad, 16-Bit, High Accuracy, Serial Input, Bipolar Voltage Output DAC |

| AD5764RASUZ-REEL7 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete Quad, 16-Bit, High Accuracy, Serial Input, Bipolar Voltage Output DAC |

| AD5764RBSUZ | 功能描述:IC DAC 16BIT QUAD VOUT 32-TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):* |

发布紧急采购,3分钟左右您将得到回复。