- 您现在的位置:买卖IC网 > PDF目录10674 > AD7682BCPZ (Analog Devices Inc)IC ADC 16BIT 4CH 250KSPS 20LFCSP PDF资料下载

参数资料

| 型号: | AD7682BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/32页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT 4CH 250KSPS 20LFCSP |

| 产品培训模块: | Power Line Monitoring |

| 产品变化通告: | Startup Circuitry Design Improvement Change 15/April/2009 |

| 标准包装: | 1 |

| 系列: | PulSAR® |

| 位数: | 16 |

| 采样率(每秒): | 250k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 21mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 20-LFCSP-VQ |

| 包装: | 托盘 |

| 输入数目和类型: | 8 个单端,单极;4 个差分,双极;4 个伪差分,双极 |

| 产品目录页面: | 778 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

Data Sheet

AD7682/AD7689

Rev. D | Page 27 of 32

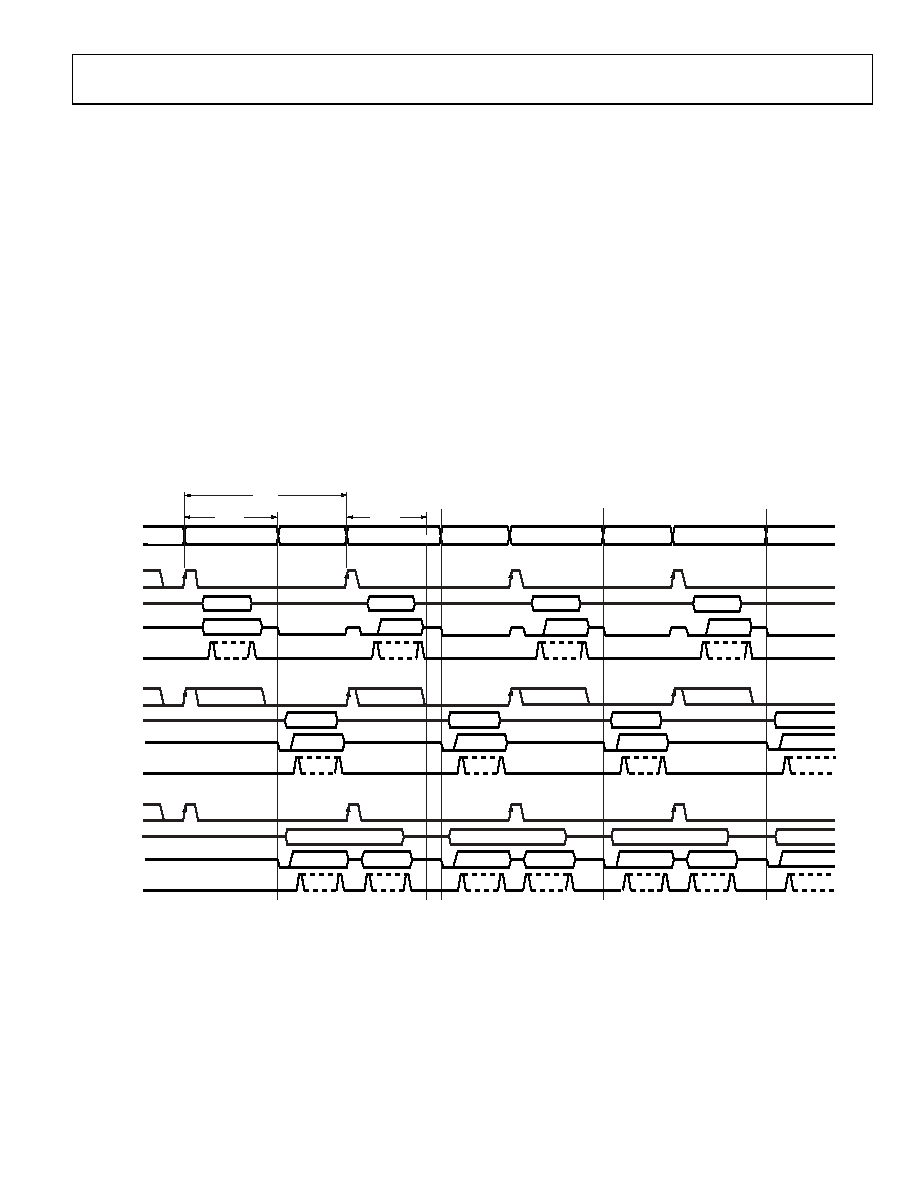

GENERAL TIMING WITH A BUSY INDICATOR

Figure 38 details the timing for all three modes: read/write

during conversion (RDC), read/write after conversion (RAC),

and read/write spanning conversion (RSC). Note that the gating

item for both CFG and data readback is at the end of conversion

(EOC). As detailed previously, the data access should occur up

to safe data reading/writing time, tDATA. If the full CFG word is

not written to prior to EOC, it is discarded and the current

configuration remains.

At the EOC, if CNV is low, the busy indicator is enabled. In

addition, to generate the busy indicator properly, the host must

assert a minimum of 17 SCK falling edges to return SDO to high

impedance because the last bit on SDO remains active. Unlike the

case detailed in the Read/Write Spanning Conversion Without a

Busy Indicator section, if the conversion result is not read out

fully prior to EOC, the last bit clocked out remains. If this bit is

low, the busy signal indicator cannot be generated because the

busy generation requires either a high impedance or a remaining

bit high-to-low transition. A good example of this occurs when

an SPI host sends 16 SCKs because these are usually limited to

8-bit or 16-bit bursts; thus the LSB remains. Because the transi-

greater), the LSB is low 50% of the time. For this interface, the SPI

host needs to burst 24 SCKs, or a QSPI interface can be used and

programmed for 17 SCKs.

The SCK can idle high or low depending on the CPOL and

CPHA settings if SPI is used. A simple solution is to use CPOL =

CPHA = 1 (not shown) with SCK idling high.

From power-up, in any read/write mode, the first three conver-

sion results are undefined because a valid CFG does not take

place until the 2nd EOC; thus, two dummy conversions are

required. Also, if the state machine writes the CFG during the

power-up state (RDC shown), the CFG register needs to be

rewritten again at the next phase. Note that the first valid data

occurs in Phase (n + 1) when the CFG register is written during

Phase (n 1).

ACQUISITION

(n – 1) UNDEFINED

ACQUISITION

(n)

ACQUISITION

(n + 1)

ACQUISITION

(n + 2)

PHASE

POWER

UP

EOC

START OF CONVERSION

(SOC)

EOC

CONVERSION

(n)

CONVERSION

(n + 1)

CONVERSION

(n – 2) UNDEFINED

07

35

3-

04

4

tCONV

tCYC

tDATA

CNV

DIN

RDC

RAC

RSC

SDO

NOTES

1. CNV MUST BE LOW PRIOR TO THE END OF CONVERSION (EOC) TO GENERATE THE BUSY INDICATOR.

2. A TOTAL OF 17 SCK FALLING EDGES ARE REQUIRED TO RETURN SDO TO HIGH-Z. IF CFG READBACK IS ENABLED,

A TOTAL OF 31 SCK FALLING EDGES IS REQUIRED TO RETURN SDO TO HIGH-Z.

DATA (n)

DATA (n – 1)

XXX

DATA (n – 2)

XXX

DATA (n – 2)

XXX

DATA (n – 2)

XXX

DATA (n – 2)

XXX

DATA (n – 1)

XXX

DATA (n – 1)

XXX

DATA (n – 1)

XXX

DATA (n – 3)

XXX

DIN

SDO

DATA (n + 1)

DATA (n)

DATA (n + 1)

DIN

CFG (n)

CFG (n + 2)

CFG (n + 1)

CFG (n + 3)

SDO

SCK

1

SCK

1n

n + 1

17

1

n

n + 1

17

1

n

n + 1

17

SCK

1

XXX

NOTE 1

NOTE 2

CFG (n)

CFG (n + 1)

CFG (n + 2)

CFG (n)

CFG (n + 1)

CFG (n + 2)

CFG (n + 3)

CONVERSION

(n – 1) UNDEFINED

相关PDF资料 |

PDF描述 |

|---|---|

| AD7794BRUZ | IC ADC 24BIT SIG-DEL 6CH 24TSSOP |

| AD7689ACPZ | IC ADC 16BIT 250KSPS 8CH 20LFCSP |

| LTC1598CG#PBF | IC A/D CONV 12BIT SRL 8CH 24SSOP |

| KA339A | IC COMPARATOR QUAD 14-DIP |

| KA339 | IC COMPARATOR QUAD 14-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7682BCPZRL7 | 功能描述:IC ADC 16BIT 4CH 250KSPS 20LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:PulSAR® 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7683 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 100 kSPS PulSAR ADC in MSOP/QFN |

| AD7683ACPZRL | 功能描述:IC ADC 16BIT SRL 100KSPS 8LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:PulSAR® 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7683ACPZRL7 | 功能描述:IC ADC 16BIT 100KSPS 8LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:PulSAR® 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7683ARM | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 16-bit Serial 8-Pin MSOP Tube |

发布紧急采购,3分钟左右您将得到回复。