参数资料

| 型号: | AD7760BSVZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/37页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT 2.5MSPS 64TQFP |

| 标准包装: | 1,500 |

| 位数: | 24 |

| 采样率(每秒): | 2.5M |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 958mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-TQFP 裸露焊盘 |

| 供应商设备封装: | 64-TQFP-EP(10x10) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个差分,单极;1 个差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

AD7760

Rev. A | Page 21 of 36

INVALID DATA

MOD DATA M

MOD DATA M + 1

MOD D...

t9

t10

t20

DRDY

D[0:15]

MCLK

CS, RD/WR

t11

t19

t14

0

497

5-

0

52

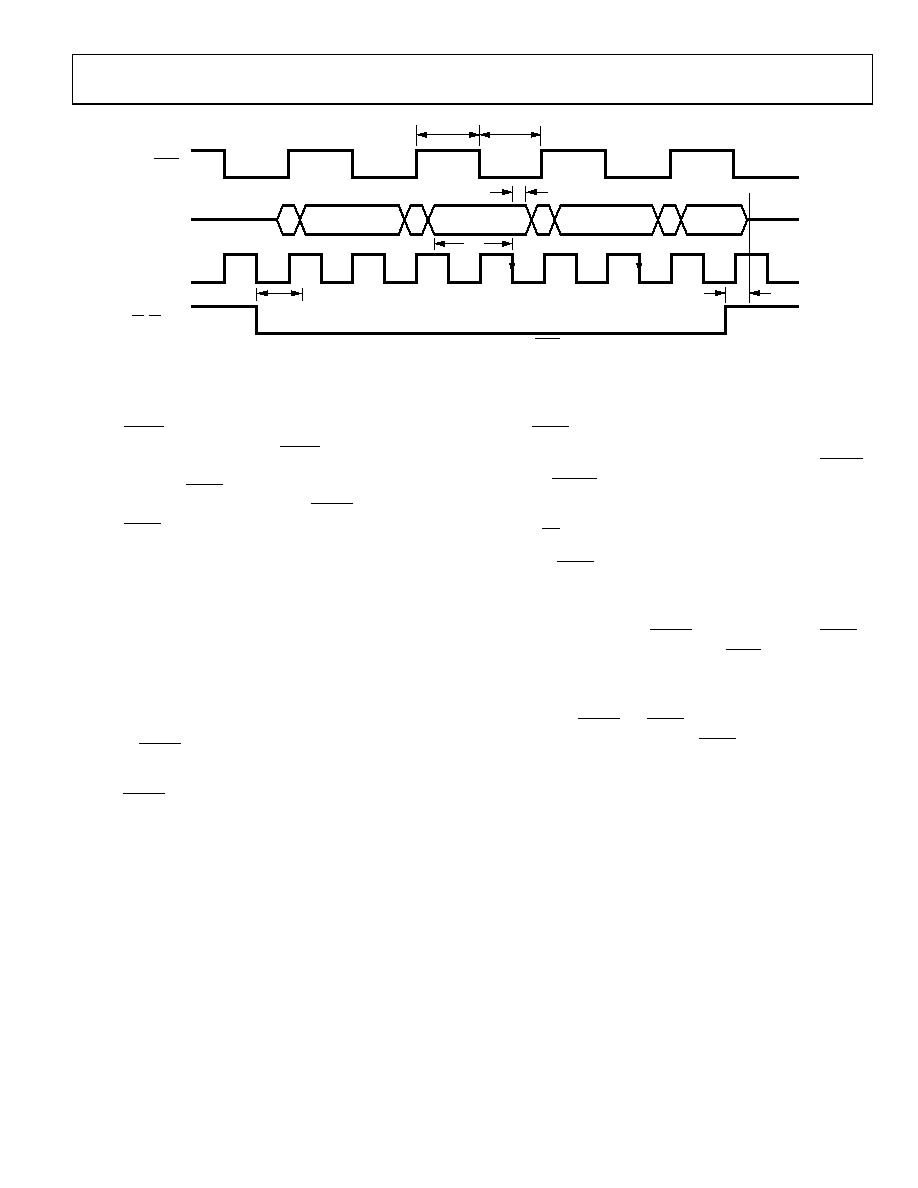

Figure 45. AD7760 Modulator Output Mode (CDIV = 0, n is odd)

In the case where n is an odd number of MCLK cycles, the

modulator data output on Pins D [15:0] is output on the rising

edge of DRDY. In this case, the modulator data should be read

on the falling edge of MCLK when DRDY is logic low. Figure 45

shows timing details to be used when reading the modulator

output data where CDIV = 0 and there is an odd number of

MCLK cycles between the rising edge of RESET and the rising

edge of SYNC. The edge of MCLK that should be used under

these conditions is illustrated in Figure 45 by arrows on the

MCLK falling edges in question.

USING THE AD7760

IN MODULATOR OUTPUT MODE

The following is the recommended sequence for powering up

and using the AD7760:

1.

Apply power.

2.

Start the clock oscillator, applying MCLK.

3.

Take RESET low for a minimum of one MCLK cycle.

4.

Wait a minimum of two MCLK cycles after the rising edge

of RESET.

5.

Write to Control Register 2 to power up the ADC and the

differential amplifier as required. The correct clock divider

(CDIV) ratio should be programmed at this time.

6.

Write to Control Register 1 to set the bypass filter bits, BYP F1

and BYP F3, and the decimation rate bits, DEC [2:0], to 0.

7.

Wait a minimum of six MCLK cycles after the rising edge

of CS has been released.

8.

Take SYNC low for a minimum of four MCLK cycles, if

required, to synchronize multiple parts.

Using this sequence results in an even number of MCLK cycles

between the rising edge of RESET and the rising edge of SYNC.

Therefore, when using this sequence with CDIV = 0, the interface

timing shown in Figure 43 should be implemented.

Note that whether the number of MCLK cycles between the

rising edge of RESET and SYNC is odd or even is irrelevant

when the AD7760 is operated with CDIV = 1.

When using the AD7760 in modulator output mode, the offset,

gain, and overrange registers are not operational. The only

registers that can be used are Control Register 1 and Control

Register 2.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7762BSVZ-REEL | IC ADC 24BIT 625KSPS 64TQFP |

| AD7763BSVZ | IC ADC 24BIT SRL 625KSPS 64TQFP |

| AD7764BRUZ-REEL7 | IC ADC 24BIT S/D 312KSPS 28TSSOP |

| AD7765BRUZ-REEL7 | IC ADC 24BIT S/D 156KSPS 28TSSOP |

| AD7766BRUZ-RL7 | IC ADC 24BIT 128KSPS SAR 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7761BSTZ | 功能描述:16 Bit Analog to Digital Converter 8 Input 8 Sigma-Delta 64-LQFP (10x10) 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 位数:16 采样率(每秒):256k 输入数:8 输入类型:差分 数据接口:SPI 配置:ADC 无线电 - S/H:ADC:- A/D 转换器数:8 架构:三角积分 参考类型:外部 电压 - 电源,模拟:2 V ~ 5.5 V 电压 - 电源,数字:- 特性:同步采样 工作温度:-40°C ~ 105°C 封装/外壳:64-LQFP 供应商器件封装:64-LQFP(10x10) 标准包装:1 |

| AD7761BSTZ-RL | 功能描述:16 Bit Analog to Digital Converter 8 Input 8 Sigma-Delta 64-LQFP (10x10) 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:有效 位数:16 采样率(每秒):256k 输入数:8 输入类型:差分 数据接口:SPI 配置:ADC 无线电 - S/H:ADC:- A/D 转换器数:8 架构:三角积分 参考类型:外部 电压 - 电源,模拟:2 V ~ 5.5 V 电压 - 电源,数字:- 特性:同步采样 工作温度:-40°C ~ 105°C 封装/外壳:64-LQFP 供应商器件封装:64-LQFP(10x10) 标准包装:1,500 |

| AD7762 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 8.5 mW, 109 dB, 128/64/32 kSPS ADCs |

| AD77628SVZ | 制造商:Analog Devices 功能描述: |

| AD7762BCP | 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 625KSPS 24BIT PARALLEL 48LFCSP - Bulk |

发布紧急采购,3分钟左右您将得到回复。