- 您现在的位置:买卖IC网 > PDF目录10160 > AD7763BSVZ-REEL (Analog Devices Inc)IC ADC 24BIT S/D 625KSPS 64-TQFP PDF资料下载

参数资料

| 型号: | AD7763BSVZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/33页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT S/D 625KSPS 64-TQFP |

| 标准包装: | 1,500 |

| 位数: | 24 |

| 采样率(每秒): | 625k |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 955.5mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-TQFP 裸露焊盘 |

| 供应商设备封装: | 64-TQFP-EP(10x10) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个差分,单极;1 个差分,双极 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

Data Sheet

AD7763

Rev. B | Page 9 of 32

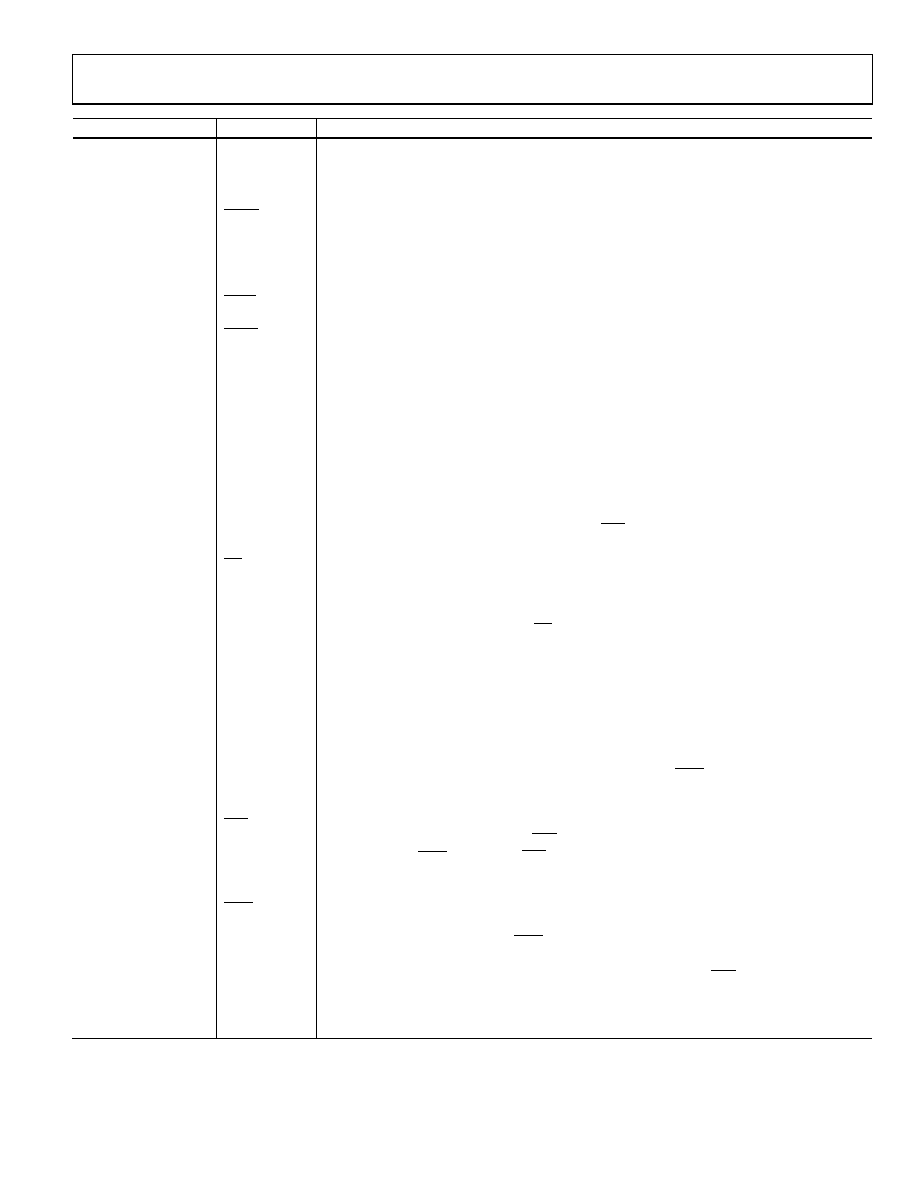

Pin No.

Mnemonic

Description

8

DECAPA

Decoupling Pin. A 100 nF capacitor must be inserted between this pin and AGND1.

30

DECAPB

Decoupling Pin. A 33 pF capacitor must be inserted between this pin and AGND3.

17

RBIAS

Bias Current Setting. A resistor must be inserted between this pin and AGND.

See the Bias Resistor Selection section.

37

RESET

A falling edge on this pin resets all internal digital circuitry. Holding this pin low

keeps the AD7763 in a reset state.

3

MCLK

Master Clock Input. A low jitter digital clock must be applied to this pin. The output data rate

depends on the frequency of this clock. See the Clocking the AD7763 section.

2

MCLKGND

Master Clock Ground Sensing Pin.

36

SYNC

Synchronization Input. A falling edge on this pin resets the internal filter. This can be used

to synchronize multiple devices in a system.

38

DRDY

Data Ready Output. Each time new conversion data is available, an active low pulse,

ICLK period wide, is produced on this pin. See the AD7763 Interface section.

39, 40, 45

SH2:0

Share Pins 2:0. For multiple AD7763 devices sharing a common serial bus. Each device is wired

with the binary value that represents the number of devices sharing the serial bus. SH2 is the

MSB. See the Sharing the Serial Bus section.

46 to 48

ADR2:0

Address 2:0. Allows multiple AD7763 devices to share a common serial bus. Each device must be

programmed with an individual address using these three pins. See the Sharing the Serial Bus

section.

49

SCP

Serial Clock Polarity. Determines on which edge of SCO the data bits are clocked out and on

which edge they are valid. All timing diagrams are shown with SCP = 0, and all SCO edges

shown should be inverted for SCP = 1.

50

SDL

Serial Data Latch. A pulse is output on this pin after every 16 data bits. The pulse is one SCO

period wide and can be used in conjunction with FSO as an alternative framing method for

serial transfers requiring a framing signal more frequent than every 32 bits.

51

FSI

Frame Sync In. The status of this pin is checked on the falling edge of SCO. If this pin is low, then

the first data bit is latched in on the next SCO falling edge when SCP = 0 or on the rising edge of

SCO if SCP = 1.

52

SDI

Serial Data In. The first data bit (MSB) must be valid on the next SCO falling edge when SCP = 0

(or SCO rising edge SCP = 1) after the FSI event has been latched. Each write requires 32 bits: the

ALL bit, 3 address bits, and 12 register address bits, followed by the remaining 16 bits of data to

be written to the device.

54

SDO

Serial Data Out. Address, status, and data bits are clocked out on this line during each serial

transfer.

If SCP = 0, each bit is clocked out on an SCO rising edge and is valid on the falling edge. When

the I2S pin is set to logic high, this pin outputs the signal defined as SD in the I2S bus

specification. See the Reading Data Using the I2S Interface section for details.

55

SCO

Serial Clock Out. This clock signal is derived from the internal ICLK signal. The frequency of SCO

is equal to either ICLK or ICLK/2, depending on the state of the CDIV and SCR pins (see the

56

FSO

Frame Sync Out. This signal frames the serial data output and is 32 SCO periods wide. The

exception to the framing behavior of FSO occurs in decimate × 32 mode, where, for certain

combinations of CDIV and SCR, the FSO signal is constantly logic low. See the Reading Data

58

CDIV

Clock Divider. This pin is used to select the ratio of MCLK to ICLK. See the AD7763 Interface

section.

60

SCR

Serial Clock Rate. This pin and the CDIV pin program the SCO frequency (see Table 7).

61

I2S

I2S Select. A Logic 1 on this pin changes the serial data-out mode from SPI to I2S. The SDO pin

outputs as the SD signal, the SCO pin outputs the SCK signal, and the FSO pin outputs the WS

See the Reading Data Using the I2S Interface section for further details.

EPAD

Exposed Pad. Connect the exposed pad to AGNDx with six to eight vias.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27468T11F4SC | CONN RCPT 4POS JAM NUT W/SCKT |

| MS3106R28-12SX | CONN PLUG 26POS STRAIGHT W/SCKT |

| 23282-31SG-350 | CONN PLUG 31POS CABLE SKT |

| VI-B3J-MW-F4 | CONVERTER MOD DC/DC 36V 100W |

| MS3106R28-12S | CONN PLUG 26POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7764 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 8.5 mW, 109 dB, 128/64/32 kSPS ADCs |

| AD7764_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 312 kSPS, 109 dB ヒ-ツ ADC with On-Chip Buffers and Serial Interface |

| AD7764BRUZ | 功能描述:IC ADC 24BIT S/D 312KSPS 28TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| AD7764BRUZ-REEL7 | 功能描述:IC ADC 24BIT S/D 312KSPS 28TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7765 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 8.5 mW, 109 dB, 128/64/32 kSPS ADCs |

发布紧急采购,3分钟左右您将得到回复。