- 您现在的位置:买卖IC网 > PDF目录8657 > AD9114BCPZRL7 (Analog Devices Inc)IC DAC DUAL 8BIT LO PWR 40LFCSP PDF资料下载

参数资料

| 型号: | AD9114BCPZRL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 40/52页 |

| 文件大小: | 0K |

| 描述: | IC DAC DUAL 8BIT LO PWR 40LFCSP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 750 |

| 系列: | TxDAC® |

| 位数: | 8 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 232mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 4 电流,单极 |

| 采样率(每秒): | 125M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Data Sheet

AD9114/AD9115/AD9116/AD9117

Rev. C | Page 45 of 52

5. Check if the self-calibration has completed by reading

Bit 6 (CALSTATI) and Bit 7 (CALSTATQ) in Register 0x0F.

Logic 1 indicates that the calibration has completed.

6. When the self-calibration has completed, write 0x00 to

Register 0x12.

7. Disable the calibration clock by clearing Bit 3 (CALCLK)

in Register 0x0E.

The AD9114/AD9115/AD9116/AD9117 allow reading and

writing of the calibration coefficients. There are 32 coefficients

in total. The read/write feature of the coefficients can be useful for

improving the results of the self-calibration routine by averaging

the results of several self-calibration cycles and loading the

averaged results back into the device.

To read the calibration coefficients, use the following steps:

1. Select which DAC core to read by setting either Bit 4

(CALSELI) for the I DAC or Bit 5 (CALSELQ) for the

Q DAC in Register 0x0E. Write the address of the first

coefficient (0x01) to Register 0x10.

2. Set Bit 2 (SMEMRD) in Register 0x12 by writing 0x04 to

Register 0x12.

3. Read the 6-bit value of the first coefficient by reading the

contents of Register 0x11.

4. Clear the SMEMRD bit by writing 0x00 to Register 0x12.

5. Repeat Step 2 through Step 4 for each of the remaining 31

coefficients by incrementing the address by 1 for each read.

6. Deselect the DAC core by clearing either Bit 4 (CALSELI)

for the I DAC and/or Bit 5 (CALSELQ) for the Q DAC in

Register 0x0E.

To write the calibration coefficients to the device, use the

following steps:

1. Select which DAC core to write to by setting either Bit 4

(CALSELI) for the I DAC or Bit 5 (CALSELQ) for the

Q DAC in Register 0x0E.

2. Set Bit 3 (SMEMWR) in Register 0x12 by writing 0x08 to

Register 0x12.

3. Write the address of the first coefficient (0x01) to

Register 0x10.

4. Write the value of the first coefficient to Register 0x11.

5. Repeat Step 2 through Step 4 for each of the remaining 31

coefficients by incrementing the address by one for each write.

6. Clear the SMEMWR bit by writing 0x00 to Register 0x12.

7. Deselect the DAC core by clearing either Bit 4 (CALSELI)

for the I DAC or Bit 5 (CALSELQ) for the Q DAC in

Register 0x0E.

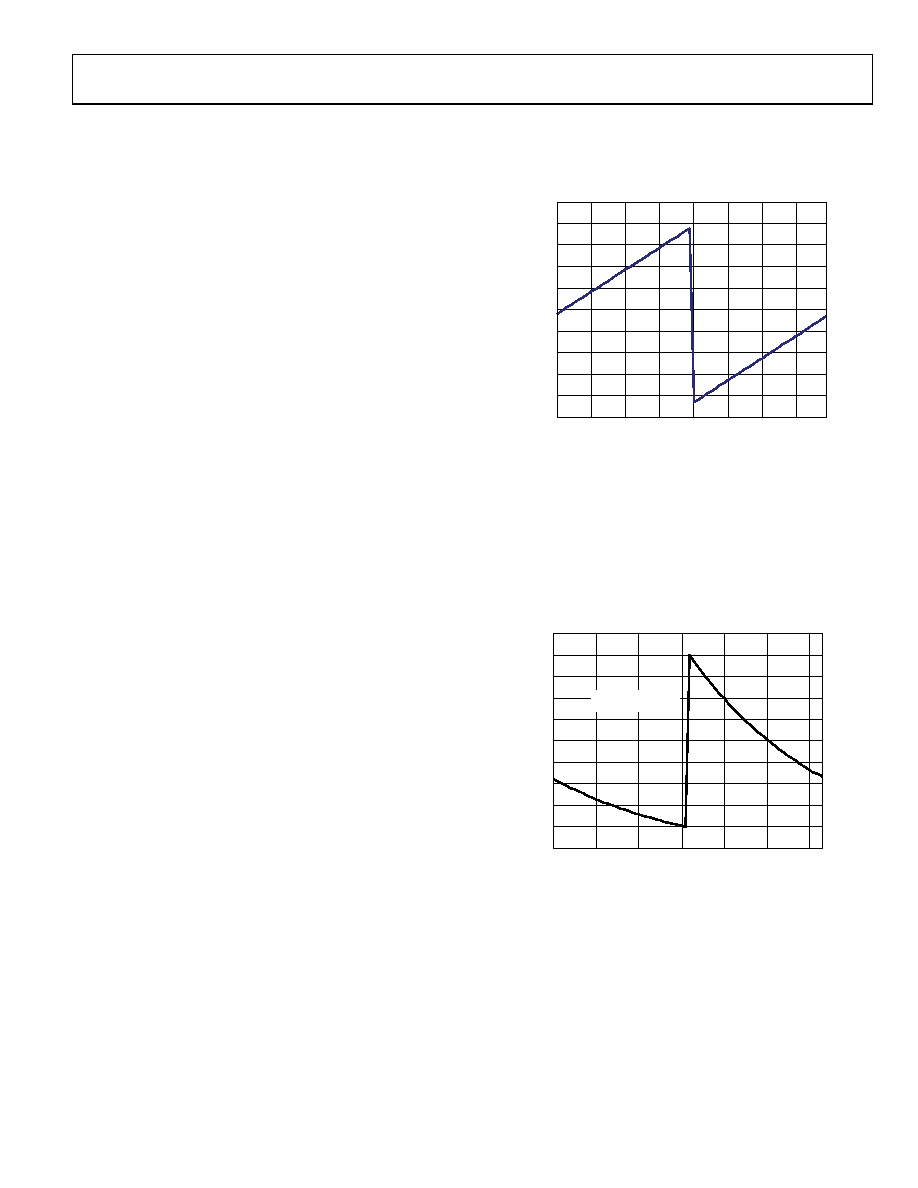

COARSE GAIN ADJUSTMENT

Option 1

A coarse full-scale output current adjustment can be achieved

using the lower six bits in Register 0x0D. This adds or subtracts

up to 20% from the band gap voltage on Pin 34 (REFIO), and

the voltage on the FSADJx resistors tracks this change. As a result,

the DAC full-scale current varies by the same amount. A secondary

effect to changing the REFIO voltage is that the full-scale voltage in

the AUXDAC also changes by the same magnitude. The register

uses twos complement format, in which 011111 maximizes the

voltage on the REFIO node and 100000 minimizes the voltage.

1.30

1.25

1.20

1.15

1.10

1.05

1.00

0.95

0.90

0.85

0.80

0

8

16

24

32

40

48

56

CODE

V

RE

F

(V)

07466-

058

Figure 97. Typical VREF Voltage vs. Code

Option 2

While using the internal FSADJx resistors, each main DAC can

achieve independently controlled coarse gain using the lower six

bits of Register 0x04 (IRSET[5:0]) and Register 0x07 (QRSET[5:0]).

Unlike Coarse Gain Option 1, this impacts only the main DAC

full-scale output current. The register uses twos complement

format and allows the output current to be changed in

approximately 0.25 dB steps.

20

18

22

16

10

12

14

8

6

4

2

0

10

20

30

40

50

60

xRSET CODE

I F

(

mA)

VOUT_Q OR VOUT_I

07466-

059

Figure 98. Effect of xRSET Code

Option 3

Even when the device is in pin mode, full-scale values can be

adjusted by sourcing or sinking current from the FSADJx pins.

Any noise injected here appears as amplitude modulation of the

output. Thus, a portion of the required series resistance (at least

20 kΩ) must be installed right at the pin. A range of ±10% is

quite practical using this method.

Option 4

As in Option 3, when the device is in pin mode, both full-scale

values can be adjusted by sourcing or sinking current from the

相关PDF资料 |

PDF描述 |

|---|---|

| IDT49FCT3805QI | IC CLK BUFFER 1:5 100MHZ 20-QSOP |

| V110A15H400BG2 | CONVERTER MOD DC/DC 15V 400W |

| VI-J6Y-MY | CONVERTER MOD DC/DC 3.3V 33W |

| VI-J0H-MX-B1 | CONVERTER MOD DC/DC 52V 75W |

| VI-J6Y-MX | CONVERTER MOD DC/DC 3.3V 49.5W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9114-DPG2-EBZ | 功能描述:IC DAC DUAL 8BIT LO PWR 40LFCSP RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:TxDAC® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| AD9114-EBZ | 制造商:Analog Devices 功能描述:DUAL 8 BIT LOW POWER CONVERTER - Boxed Product (Development Kits) |

| AD9115 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual, 8-/10-/12-/14-Bit Low Power Digital-to-Analog Converters |

| AD91151Z | 制造商:Analog Devices 功能描述: |

| AD91154Z | 制造商:Analog Devices 功能描述:SCREENED DSP PART - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。